ICS671-15

ICS671-15 is Low Skew Buffer manufactured by Integrated Circuit Systems.

ZERO DELAY, LOW SKEW BUFFER

Description

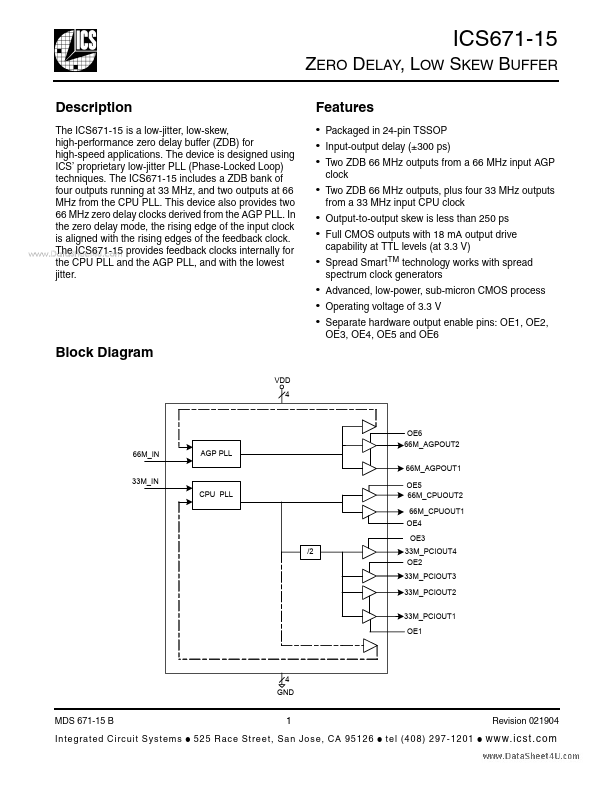

The ICS671-15 is a low-jitter, low-skew, high-performance zero delay buffer (ZDB) for high-speed applications. The device is designed using ICS’ proprietary low-jitter PLL (Phase-Locked Loop) techniques. The ICS671-15 includes a ZDB bank of four outputs running at 33 MHz, and two outputs at 66 MHz from the CPU PLL. This device also provides two 66 MHz zero delay clocks derived from the AGP PLL. In the zero delay mode, the rising edge of the input clock is aligned with the rising edges of the feedback clock. The ICS671-15 provides feedback clocks internally for .. the CPU PLL and the AGP PLL, and with the lowest...