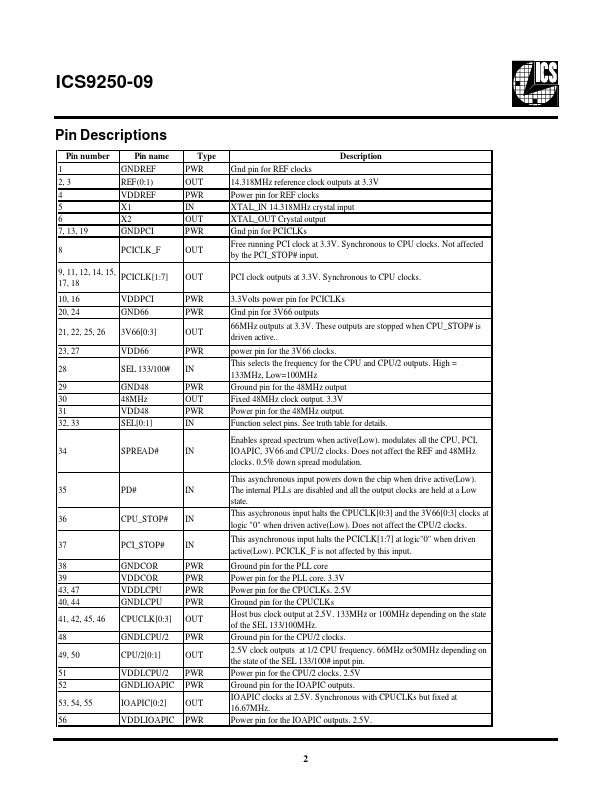

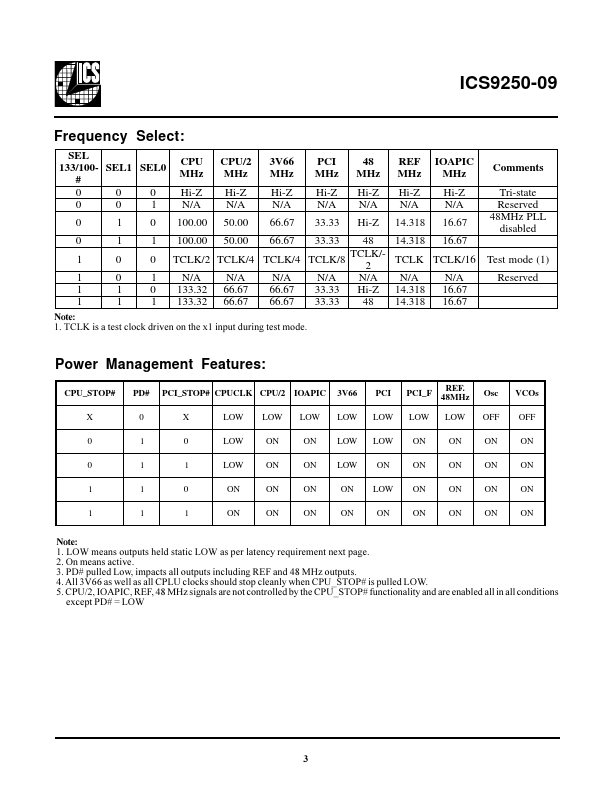

Datasheet Summary

Integrated Circuit Systems, Inc.

Frequency Timing Generator for PENTIUM II Systems

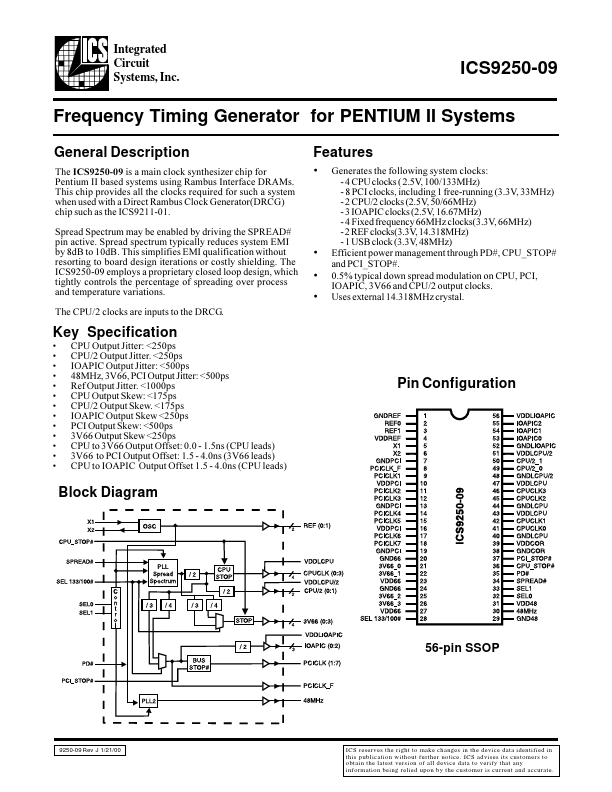

General Description

The ICS9250-09 is a main clock synthesizer chip for Pentium II based systems using Rambus Interface DRAMs. This chip provides all the clocks required for such a system when used with a Direct Rambus Clock Generator(DRCG) chip such as the ICS9211-01. Spread Spectrum may be enabled by driving the SPREAD# pin active. Spread spectrum typically reduces system EMI by 8dB to 10dB. This simplifies EMI qualification without resorting to board design iterations or costly shielding. The ICS9250-09 employs a proprietary closed loop design, which tightly controls the percentage of...