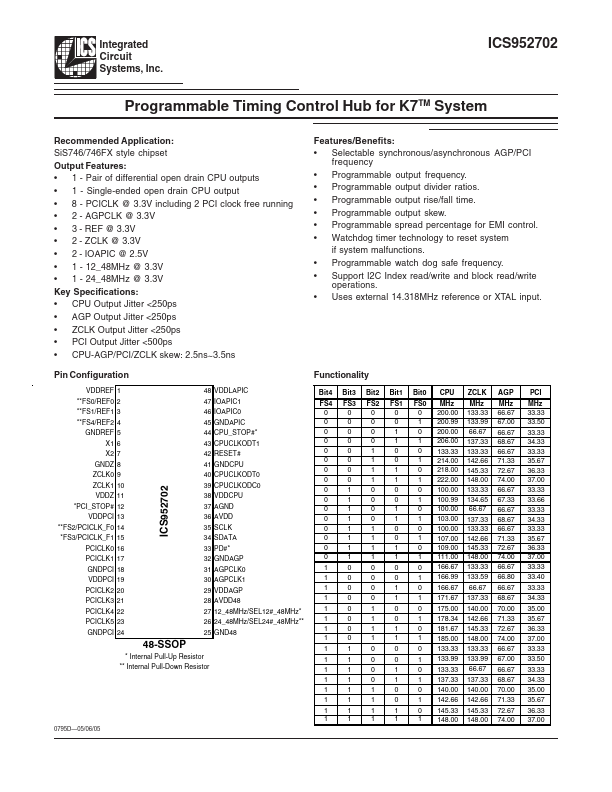

ICS952702 Key Features

- Pair of differential open drain CPU outputs

- Single-ended open drain CPU output

- PCICLK @ 3.3V including 2 PCI clock free running

- AGPCLK @ 3.3V

- REF @ 3.3V

- ZCLK @ 3.3V

- IOAPIC @ 2.5V

- 12_48MHz @ 3.3V

- 24_48MHz @ 3.3V Key Specifications

- CPU Output Jitter <250ps