M2006-12A

M2006-12A is VCSO BASED FEC CLOCK PLL WITH HITLESS SWITCHING manufactured by Integrated Circuit Systems.

- Part of the M20 comparator family.

- Part of the M20 comparator family.

DESCRIPTION

The M2006-12A is a VCSO (Voltage Controlled SAW Oscillator) based clock generator PLL designed for clock frequency translation and jitter attenuation. Clock multiplication ratios (including forward and inverse FEC) are pin-selected from pre-programming look-up tables. Includes Hitless Switching and Phase Build-out to enable SONET (GR-253) / SDH (G.813) MTIE and TDEV pliance during reference clock reselection. Hitless Switching (HS) engages when a 4ns or greater clock phase change is detected.

This phase-change triggered implementation of HS is not remended when using an unstable reference (more than 1ns jitter pk-to-pk) or when the resulting phase detector frequency is less than 5MHz.

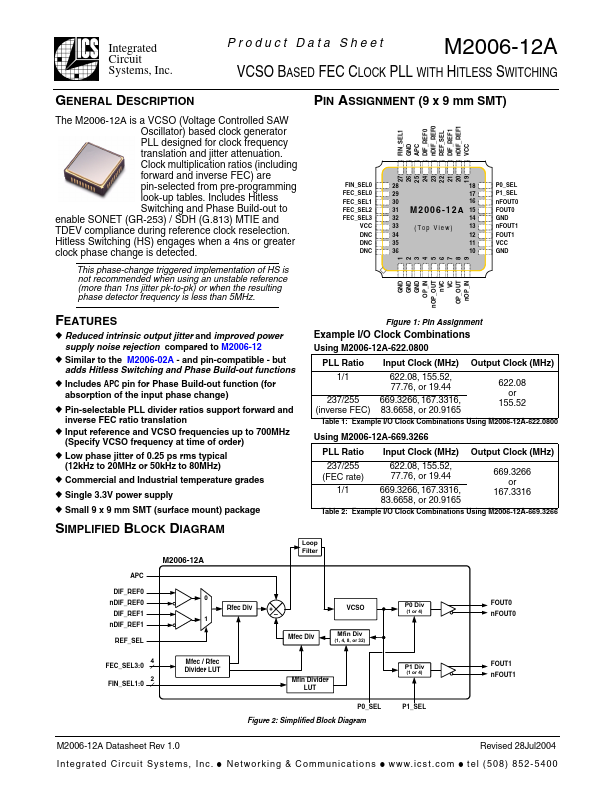

28 29 30 31 32 33 34 35 36

(Top View)

18 17 16 15 14 13 12 11 10

P0_SEL P1_SEL n FOUT0 FOUT0 GND n FOUT1 FOUT1 VCC GND

FEATURES

- Reduced intrinsic output jitter and improved power supply noise rejection pared to M2006-12

- Similar to the M2006-02A

- and pin-patible

- but adds Hitless Switching and Phase Build-out functions

- Includes APC pin for Phase Build-out function (for absorption of the input phase change)

- Pin-selectable PLL divider ratios support forward and inverse FEC ratio translation

- Input reference and VCSO frequencies up to 700MHz (Specify VCSO frequency at time of order)

- Low phase jitter of 0.25 ps rms typical (12k Hz to 20MHz or 50k Hz to 80MHz)

- mercial and Industrial temperature grades

- Single 3.3V power supply

- Small 9 x 9 mm SMT (surface mount) package PLL Ratio 1/1 237/255 (inverse FEC)

Figure 1: Pin Assignment

Example I/O Clock binations

Using M2006-12A-622.0800 Input Clock (MHz) 622.08, 155.52, 77.76, or 19.44 669.3266, 167.3316, 83.6658, or 20.9165 Output Clock (MHz) 622.08 or 155.52

Table 1: Example I/O Clock binations Using M2006-12A-622.0800

Using M2006-12A-669.3266 PLL Ratio 237/255 (FEC rate) 1/1 Input Clock (MHz) 622.08, 155.52, 77.76, or 19.44 669.3266, 167.3316, 83.6658, or 20.9165 Output Clock (MHz) 669.3266 or...