IDT74ALVCH32373

IDT74ALVCH32373 is 3.3V CMOS 32-BIT TRANSPARENT D-TYPE LATCH WITH 3-STATE OUTPUTS AND BUS-HOLD manufactured by Integrated Device Tech.

IDT74ALVCH32373 3.3V CMOS 32-BIT TRANSPARENT D-TYPE LATCH WITH 3-STATE OUTPUTS

INDUSTRIAL TEMPERATURE RANGE

3.3V CMOS 32-BIT TRANSPARENT D-TYPE LATCH WITH 3-STATE OUTPUTS AND BUS-HOLD

- 0.5 MICRON CMOS Technology

- Typical t SK(o) (Output Skew) < 250ps

- ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200p F, R = 0)

- VCC = 3.3V ± 0.3V, Normal Range

- VCC = 2.7V to 3.6V, Extended Range

- VCC = 2.5V ± 0.2V

- CMOS power levels (0.4µ W typ. static)

- Rail-to-Rail output swing for increased noise margin

- Available in 96-ball LFBGA package

Features

:

DESCRIPTION:

DRIVE Features

:

- High Output Drivers: ±24m A

- Suitable for Heavy Loads

The 32-bit transparent D-type latch is built using advanced dual metal CMOS technology. The high-speed, low-power latch is ideal for temporary storage of data. The device can be used for implementing memory address latches, I/O ports, and bus drivers. The Output Enable and Latch Enable controls are organized to operate each device as four 8-bit latches, two 16bit latches, or one 32-bit latch. Flow-through organization of signal pins simplifies layout. All inputs are designed with hysteresis for improved noise margin. The ALVCH32373 has been designed with a ±24m A output driver. This driver is capable of driving a moderate to heavy load while maintaining speed performance. The ALVCH32373 has “bus-hold” which retains the inputs’ last state whenever the input goes to a high impedance. This prevents floating inputs and eliminates the need for pull-up/down resistor.

APPLICATIONS:

- 3.3V high speed systems

- 3.3V and lower voltage puting systems

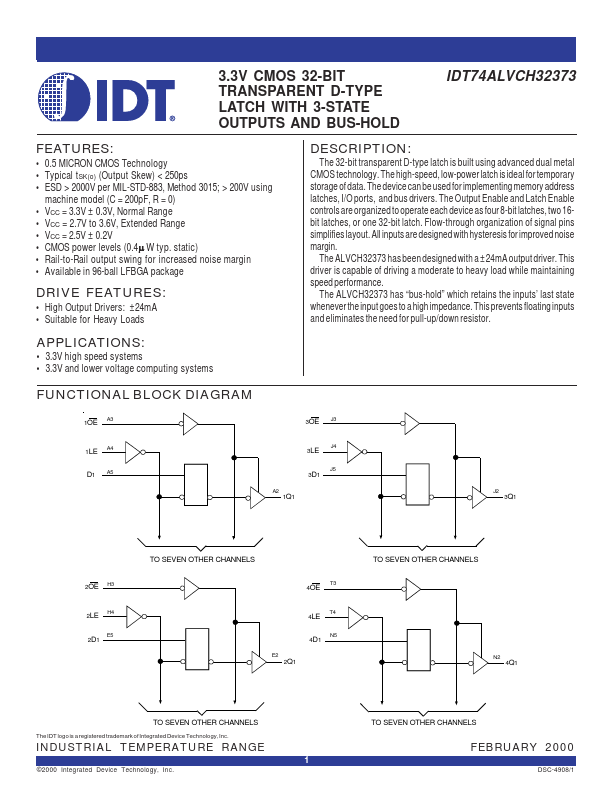

FUNCTIONAL BLOCK DIAGRAM

1OE

A3

3OE

J3

1LE

A4...