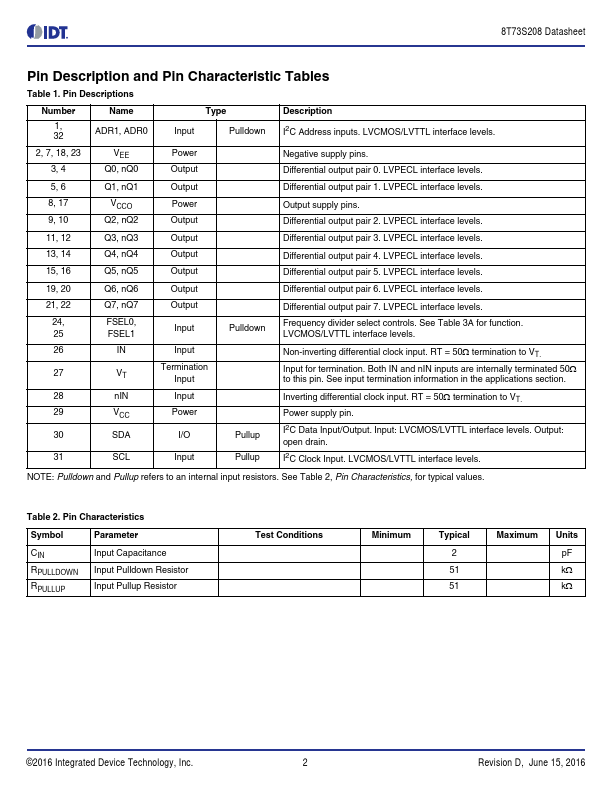

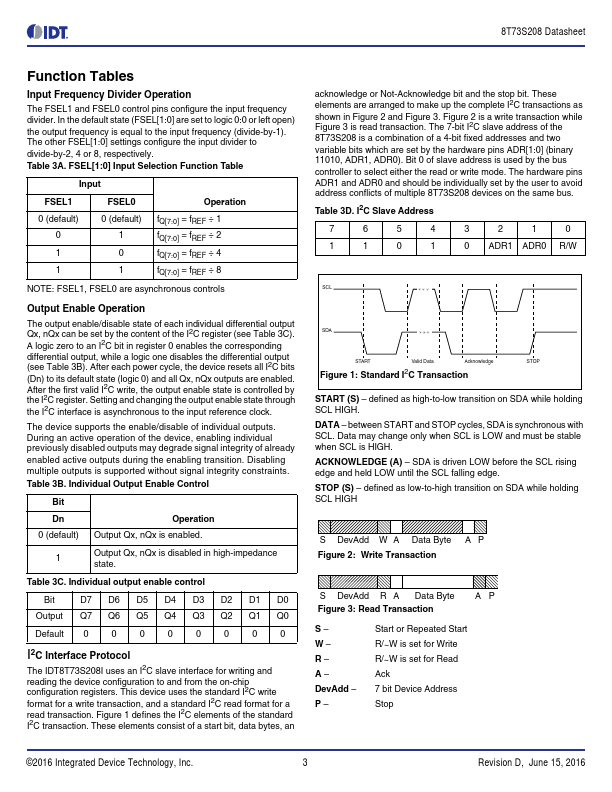

Datasheet Summary

2.5 V, 3.3 V Differential LVPECL Clock Divider and Fanout Buffer

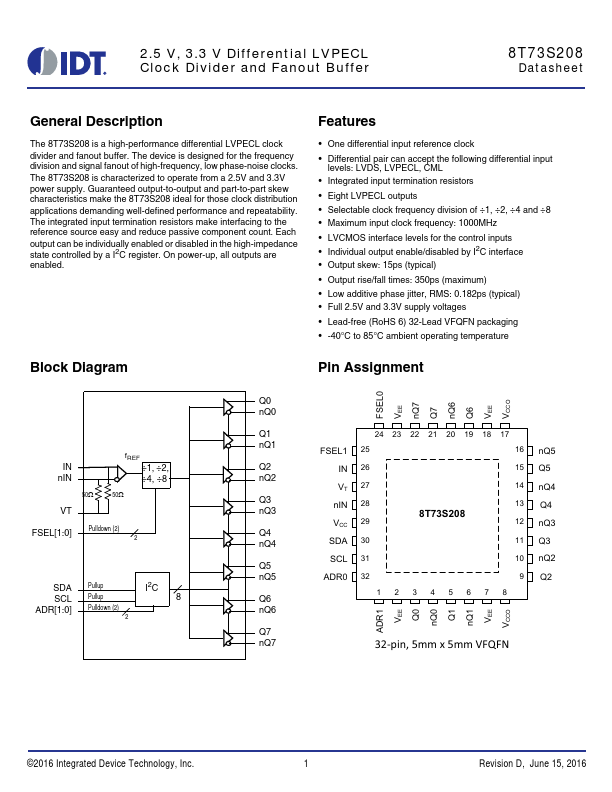

General Description

The 8T73S208 is a high-performance differential LVPECL clock divider and fanout buffer. The device is designed for the frequency division and signal fanout of high-frequency, low phase-noise clocks. The 8T73S208 is characterized to operate from a 2.5V and 3.3V power supply. Guaranteed output-to-output and part-to-part skew characteristics make the 8T73S208 ideal for those clock distribution applications demanding well-defined performance and repeatability. The integrated input termination resistors make interfacing to the reference source easy and reduce passive ponent count. Each...