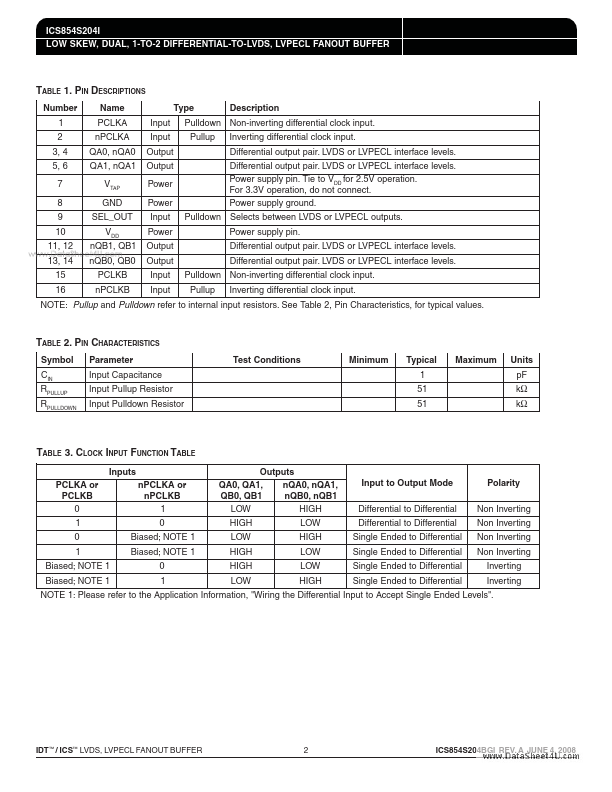

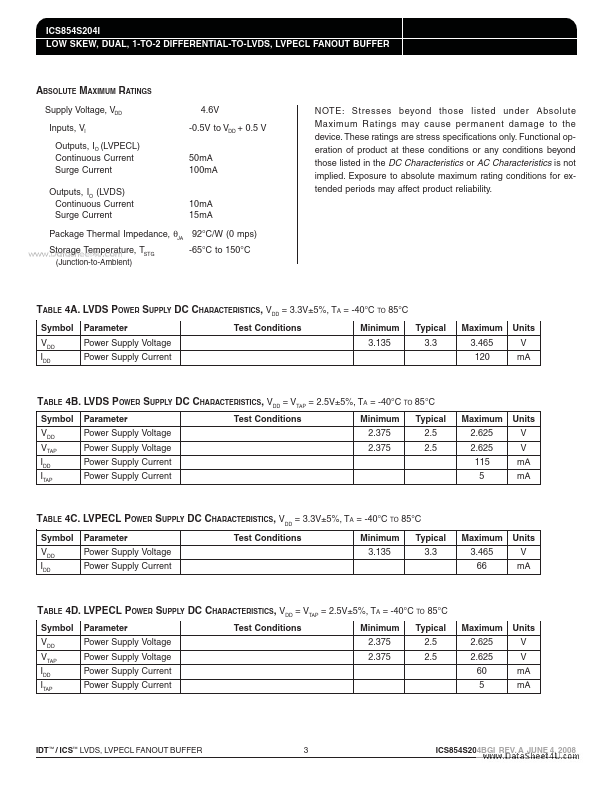

Datasheet Summary

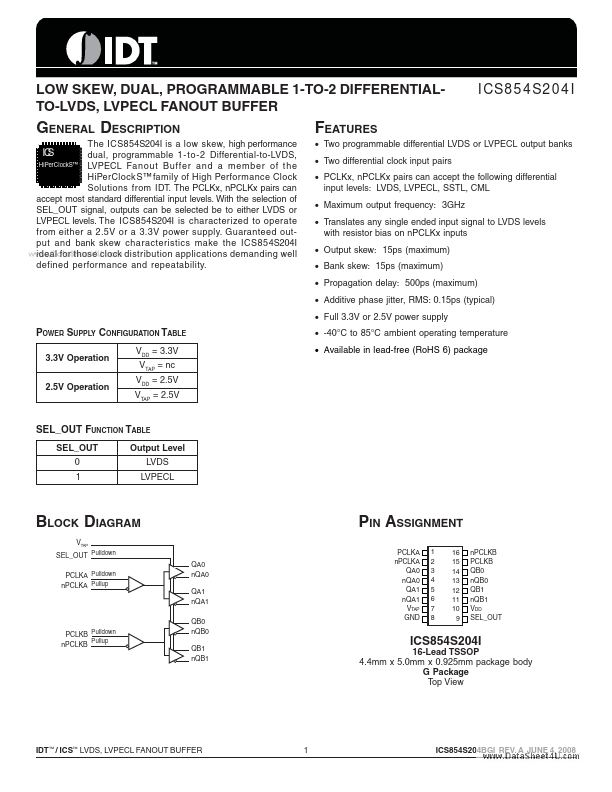

LOW SKEW, DUAL, PROGRAMMABLE 1-TO-2 DIFFERENTIALTO-LVDS, LVPECL FANOUT BUFFER

GENERAL DESCRIPTION

The ICS854S204I is a low skew, high performance IC S dual, programmable 1-to-2 Differential-to-LVDS, HiPerClockS™ LVPECL Fanout Buffer and a member of the HiPerClock S™ family of High Performance Clock Solutions from IDT. The PCLKx, nPCLKx pairs can accept most standard differential input levels. With the selection of SEL_OUT signal, outputs can be selected be to either LVDS or LVPECL levels. The ICS854S204I is characterized to operate from either a 2.5V or a 3.3V power supply. Guaranteed output and bank skew characteristics make the ICS854S204I .. ideal for...