IDT54FCT162511CT

IDT54FCT162511CT is FAST CMOS 16-BIT REGISTERED/LATCHED TRANSCEIVER WITH PARITY manufactured by Integrated Device Technology.

Integrated Device Technology, Inc.

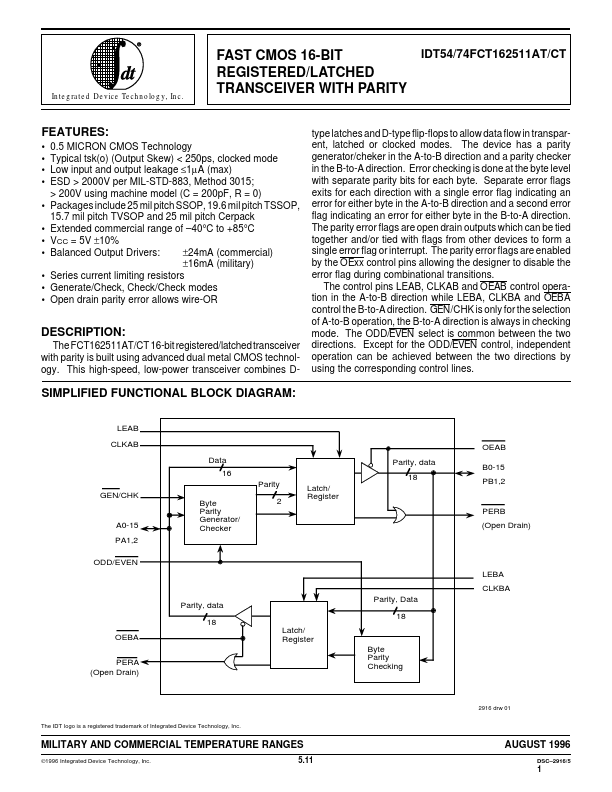

FAST CMOS 16-BIT REGISTERED/LATCHED TRANSCEIVER WITH PARITY

IDT54/74FCT162511AT/CT

Features

:

- -

- -

- -

- -

- -

- 0.5 MICRON CMOS Technology Typical tsk(o) (Output Skew) < 250ps, clocked mode Low input and output leakage ≤1µA (max) ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200pF, R = 0) Packages include 25 mil pitch SSOP, 19.6 mil pitch TSSOP, 15.7 mil pitch TVSOP and 25 mil pitch Cerpack Extended mercial range of

- 40°C to +85°C VCC = 5V ±10% Balanced Output Drivers: ±24mA (mercial) ±16mA (military) Series current limiting resistors Generate/Check, Check/Check modes Open drain parity error allows wire-OR

DESCRIPTIO...