IDT5T907

IDT5T907 is 2.5V SINGLE DATA RATE 1:10 CLOCK BUFFER TERABUFFER manufactured by Integrated Device Technology.

IDT5T907 2.5V SINGLE DATA RATE 1:10 CLOCK BUFFER TERABUFFER

INDUSTRIAL TEMPERATURE RANGE

..

2.5V SINGLE DATA RATE 1:10 CLOCK BUFFER TERABUFFER™

Features

:

- -

- -

- -

- -

- IDT5T907

DESCRIPTION:

Guaranteed Low Skew < 25ps (max) Very low duty cycle distortion High speed propagation delay < 2.5ns. (max) Up to 250MHz operation Very low CMOS power levels 1.5V VDDQ for HSTL interface Hot insertable and over-voltage tolerant inputs 3-level inputs for selectable interface Selectable HSTL, e HSTL, 1.8V / 2.5V LVTTL, or LVEPECL input interface

- Selectable differential or single-ended inputs and ten singleended outputs

- 2.5V VDD

- Available in TSSOP package

The IDT5T907 2.5V single data rate (SDR) clock buffer is a user-selectable single-ended or differential input to ten single-ended outputs buffer built on advanced metal CMOS technology. The SDR clock buffer fanout from a single or differential input to ten single-ended outputs reduces the loading on the preceding driver and provides an efficient clock distribution network. The IDT5T907 can act as a translator from a differential HSTL, e HSTL, 1.8V/2.5V LVTTL, LVEPECL, or single-ended 1.8V/2.5V LVTTL input to HSTL, e HSTL, 1.8V/2.5V LVTTL outputs. Selectable interface is controlled by 3-level input signals that may be hard-wired to appropriate high-mid-low levels. The IDT5T907 has two output banks that can be asynchronously enabled/ disabled. Multiple power and grounds reduce noise.

- Clock and signal distribution

APPLICATIONS:

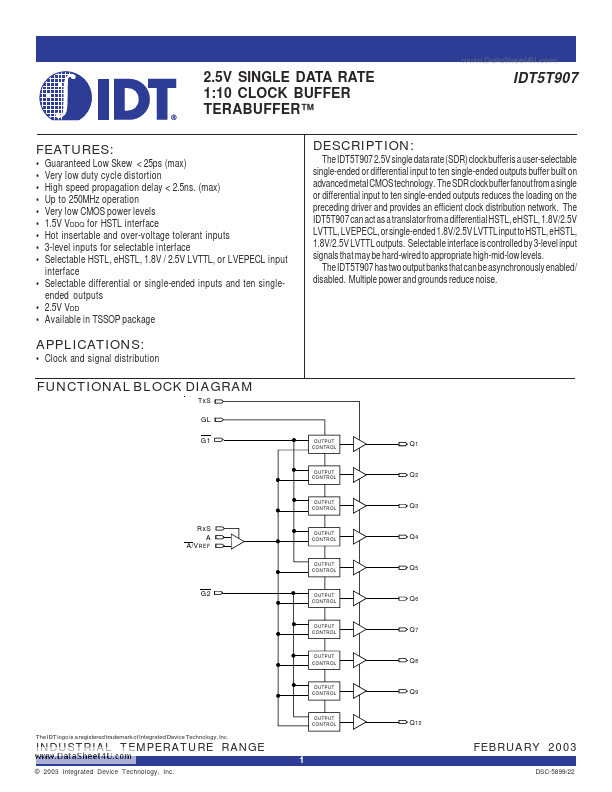

FUNCTIONAL BLOCK DIAGRAM

Tx S GL G1

O UTPUT CO NTR OL

Q1

O UTPUT CO NTR OL

Q2

O UTPUT CO NTR OL

Q3

Rx S A A/V R EF

O UTPUT CO NTR...