| Part | IDT70V28L |

|---|---|

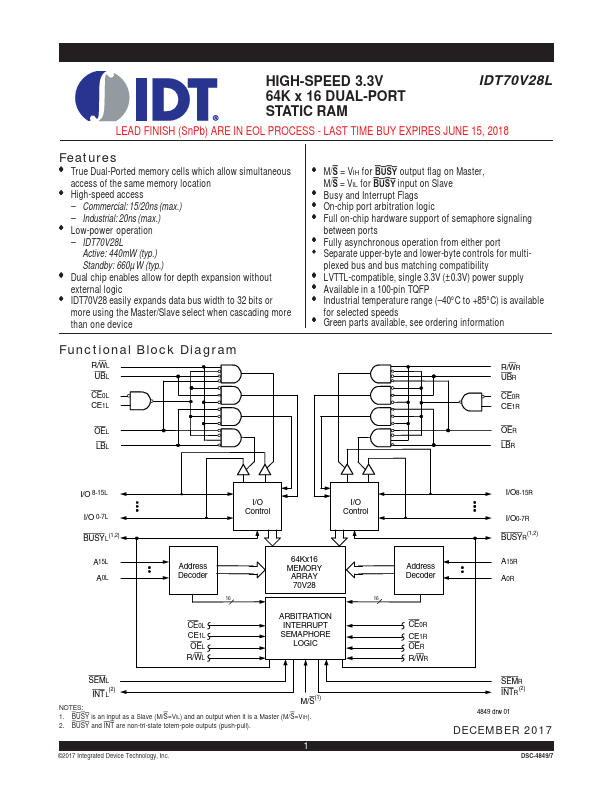

| Description | HIGH-SPEED 3.3V 64K x 16 DUAL-PORT STATIC RAM |

| Manufacturer | Integrated Device Technology |

| Size | 194.72 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| IDT70V25 | IDT | HIGH-SPEED 3.3V 8K x 18 DUAL-PORT STATIC RAM |

| IDT70V24 | IDT | HIGH-SPEED 3.3V 8K x 18 DUAL-PORT STATIC RAM |