IDT71B74

IDT71B74 is BiCMOS STATIC RAM 64K (8K x 8-BIT) CACHE-TAG RAM manufactured by Integrated Device Technology.

- Part of the IDT-71B comparator family.

- Part of the IDT-71B comparator family.

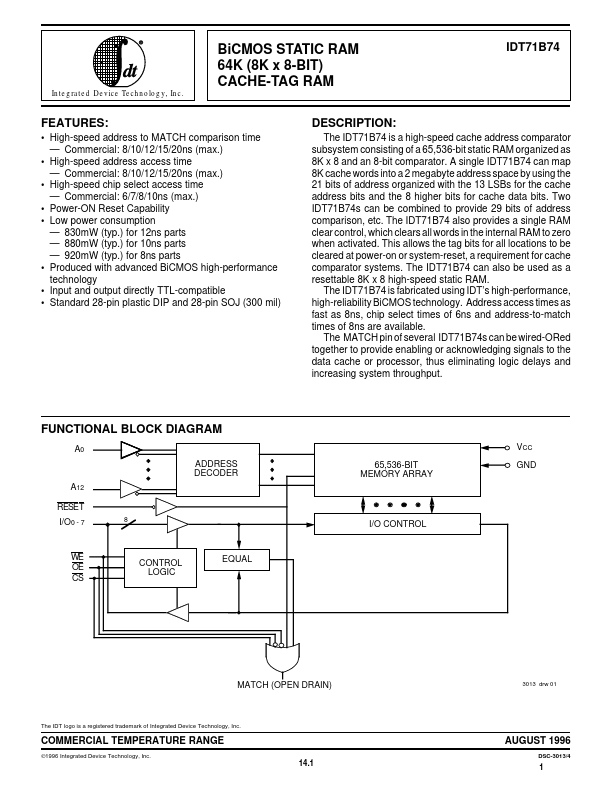

BiCMOS STATIC RAM 64K (8K x 8-BIT) CACHE-TAG RAM

Integrated Device Technology, Inc.

Features

:

- High-speed address to MATCH parison time

- mercial: 8/10/12/15/20ns (max.)

- High-speed address access time

- mercial: 8/10/12/15/20ns (max.)

- High-speed chip select access time

- mercial: 6/7/8/10ns (max.)

- Power-ON Reset Capability

- Low power consumption

- 830mW (typ.) for 12ns parts

- 880mW (typ.) for 10ns parts

- 920mW (typ.) for 8ns parts

- Produced with advanced BiCMOS high-performance technology

- Input and output directly TTL-patible

- Standard 28-pin plastic DIP and 28-pin SOJ (300 mil)

DESCRIPTION:

The IDT71B74 is a high-speed cache address parator...