IDT723666

IDT723666 is (IDT7236x6) CMOS TRIPLE BUS SyncFIFOTM manufactured by Integrated Device Technology.

CMOS TRIPLE BUS Sync FIFOTM WITH BUS-MATCHING .. 2,048 x 36 x 2 IDT723656 4,096 x 36 x 2 IDT723666 8,192 x 36 x 2 IDT723676

Features

- -

- -

- -

Memory storage capacity: IDT723656

- 2,048 x 36 x 2 IDT723666

- 4,096 x 36 x 2 IDT723676

- 8,192 x 36 x 2 Clock frequencies up to 83 MHz (8ns access time) Two independent FIFOs buffer data between one bidirectional 36-bit port and two unidirectional 18-bit ports (Port C receives and Port B transmits) 18-bit (word) and 9-bit (byte) bus sizing of 18 bits (word) on Ports B and C Select IDT Standard timing (using EFA , EFB , FFA , and FFC flag functions) or First Word Fall Through Timing (using ORA, ORB, IRA, and IRC flag functions) Programmable Almost-Empty and Almost-Full flags; each has

- -

- -

- -

- -

- -

- five default offsets (8, 16, 64, 256 and 1024) Serial or parallel programming of partial flags Big- or Little-Endian format for word and byte bus sizes Loopback mode on Port A Retransmit Capability Master Reset clears data and configures FIFO, Partial Reset clears data but retains configuration settings Mailbox bypass registers for each FIFO Free-running CLKA, CLKB and CLKC may be asynchronous or coincident (simultaneous reading and writing of data on a single clock edge is permitted) Auto power down minimizes power dissipation Available in a space-saving 128-pin Thin Quad Flatpack (TQFP) Pin patible to the lower density parts, IDT723626/3636/3646 Industrial temperature range (- 40° C to +85°C) is available

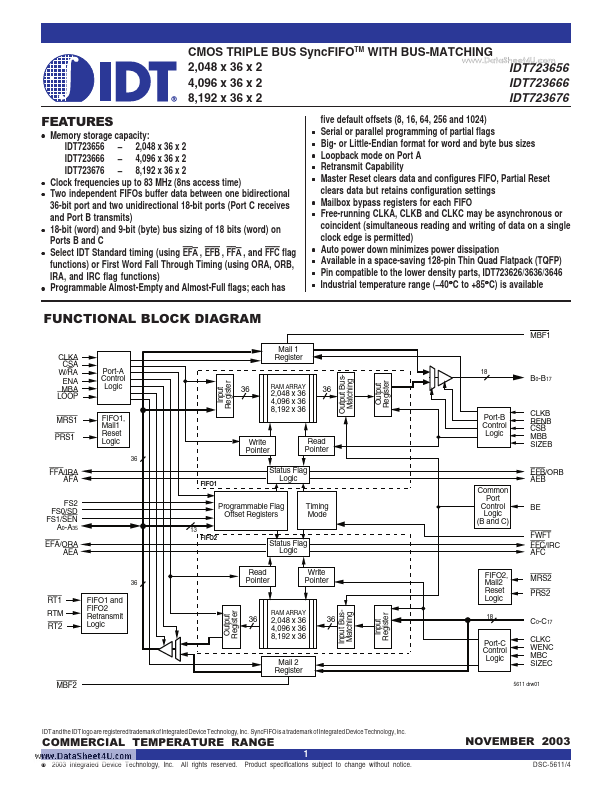

FUNCTIONAL BLOCK DIAGRAM

MBF1 CLKA CSA W/RA ENA MBA LOOP MRS1 PRS1 Mail 1 Register

Output Bus Matching

Input Register

RAM ARRAY

2,048 x 36 4,096 x 36 8,192 x 36

Output Register

Port-A Control Logic

B0-B17

FIFO1, Mail1 Reset Logic

Port-B Control Logic Write Pointer Read Pointer

CLKB RENB CSB MBB SIZEB

FFA/IRA AFA FS2 FS0/SD FS1/SEN A0-A35 EFA/ORA AEA

FIFO1

Status Flag Logic mon Port Control Logic (B and...