IDT74LVC374A

IDT74LVC374A is 3.3V CMOS OCTAL EDGE-TRIGGERED D-TYPE FLIP-FLOP manufactured by Integrated Device Technology.

..

IDT74LVC374A 3.3V CMOS OCTAL EDGE-TRIGGERED D-TYPE FLIP-FLOP

INDUSTRIAL TEMPERATURE RANGE

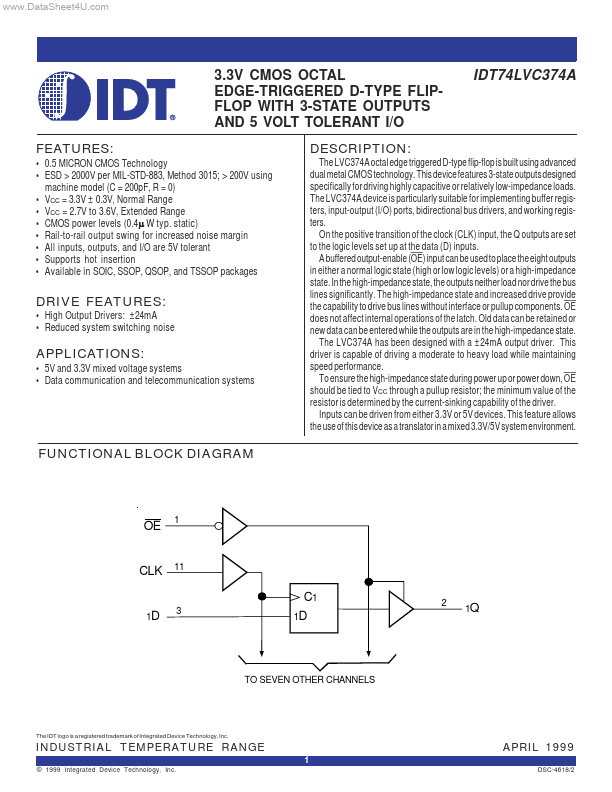

3.3V CMOS OCTAL EDGE-TRIGGERED D-TYPE FLIPFLOP WITH 3-STATE OUTPUTS AND 5 VOLT TOLERANT I/O

- 0.5 MICRON CMOS Technology

- ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200p F, R = 0)

- VCC = 3.3V ± 0.3V, Normal Range

- VCC = 2.7V to 3.6V, Extended Range

- CMOS power levels (0.4µ W typ. static)

- Rail-to-rail output swing for increased noise margin

- All inputs, outputs, and I/O are 5V tolerant

- Supports hot insertion

- Available in SOIC, SSOP, QSOP, and TSSOP packages

Features

:

DRIVE Features

:

- High Output Drivers: ±24m A

- Reduced system switching noise

APPLICATIONS:

- 5V and 3.3V mixed voltage systems

- Data munication and telemunication systems

The LVC374A octal edge triggered D-type flip-flop is built using advanced dual metal CMOS technology. This device Features

3-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads. The LVC374A device is particularly suitable for implementing buffer registers, input-output (I/O) ports, bidirectional bus drivers, and working registers. On the positive transition of the clock (CLK) input, the Q outputs are set to the logic levels set up at the data (D) inputs. A buffered output-enable (OE) input can be used to place the eight outputs in either a normal logic state (high or low logic levels) or a high-impedance state. In the high-impedance state, the outputs neither load nor drive the bus lines significantly. The high-impedance state and increased drive provide the capability to drive bus lines without interface or pullup ponents. OE does not affect internal operations of the latch. Old data can be retained or new data can be entered while the outputs are in the high-impedance state. The LVC374A has been designed with a ±24m A output driver. This driver is capable of driving a moderate to heavy load while...