Datasheet Summary

Dual Synchronous Ethernet Line Card PLL

Short Form Datasheet IDT82V3396

Features

HIGHLIGHTS

- Dual PLL chip:

- Provides node clock for ITU-T G.8261/G.8262 Synchronous Ethernet (SyncE)

- Exceeds GR-253-CORE (OC-12) and ITU-T G.813 (STM-4) jitter generation requirements

- Provides node clocks for Cellular and WLL base-station (GSM and 3G networks)

- Provides clocks for 1 Gigabit and 10 Gigabit Ethernet applications

MAIN Features

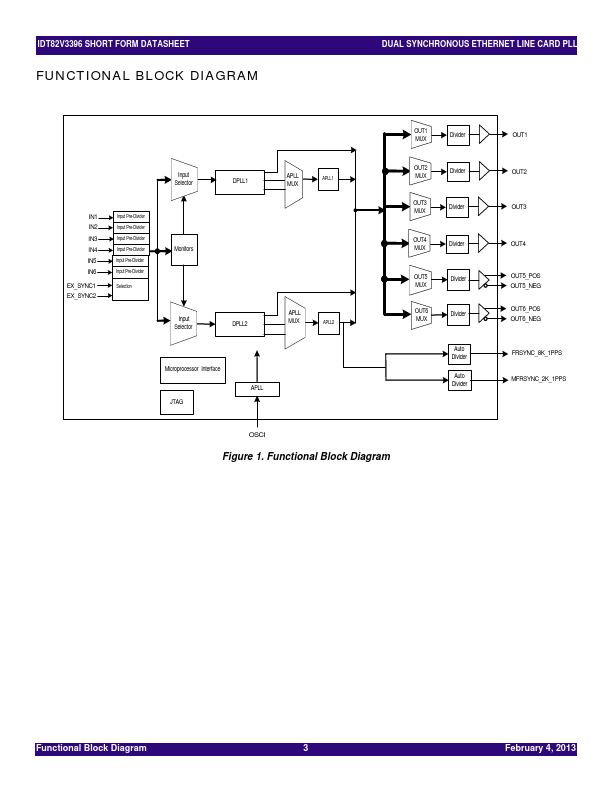

- Employs PLL architecture to feature excellent jitter performance and minimize the number of external ponents

- Integrates 2 DPLLs; one can be used on the transmit path and the other on the receive path

- Supports programmable DPLL bandwidth: 18 Hz, 35 Hz, 70...