IDT88P8344

IDT88P8344 is SPI EXCHANGE manufactured by Integrated Device Technology.

..

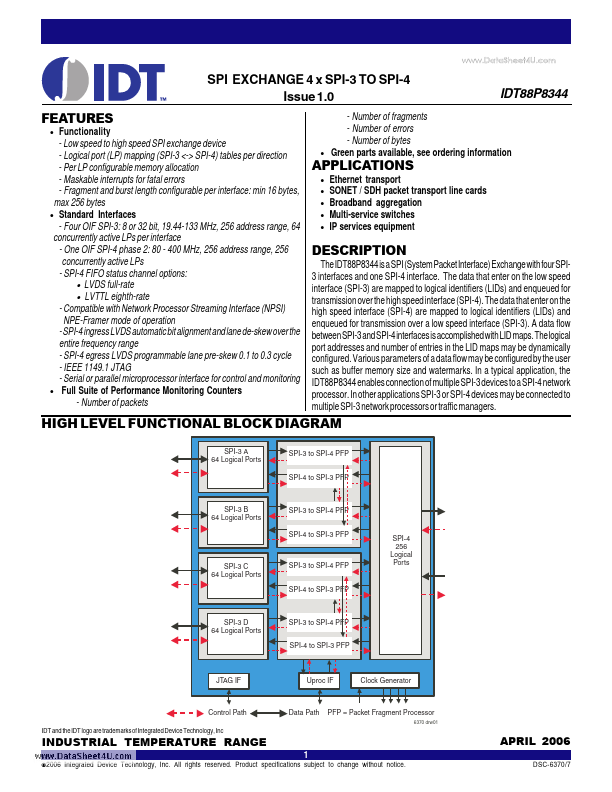

SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 Features

- IDT88P8344

Functionality

- Low speed to high speed SPI exchange device

- Logical port (LP) mapping (SPI-3 <-> SPI-4) tables per direction

- Per LP configurable memory allocation

- Maskable interrupts for fatal errors

- Fragment and burst length configurable per interface: min 16 bytes, max 256 bytes

- Standard Interfaces

- Four OIF SPI-3: 8 or 32 bit, 19.44-133 MHz, 256 address range, 64 concurrently active LPs per interface

- One OIF SPI-4 phase 2: 80

- 400 MHz, 256 address range, 256 concurrently active LPs

- SPI-4 FIFO status channel options:

- LVDS full-rate

- LVTTL eighth-rate

- patible with Network...