QS5919T Overview

Key Specifications

Package: SSOP

Pins: 28

Operating Voltage: 5 V

Max Voltage (typical range): 5.5 V

Description

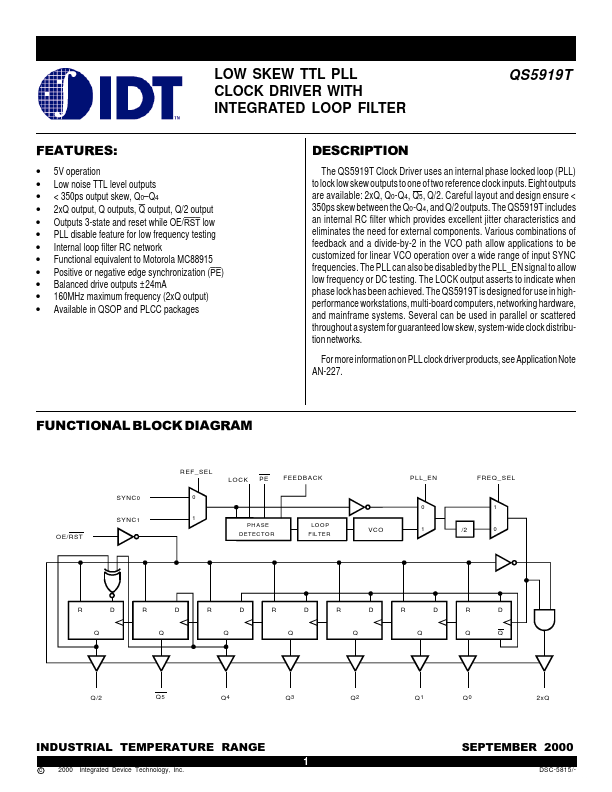

The QS5919T Clock Driver uses an internal phase locked loop (PLL) to lock low skew outputs to one of two reference clock inputs. Eight outputs are available: 2xQ, Q 0-Q4, Q5, Q/2.