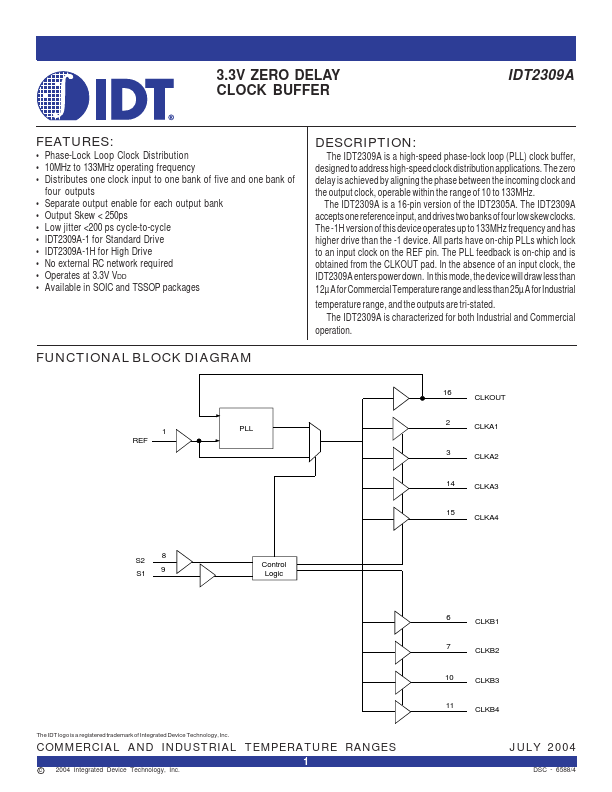

| Part | IDT2309A |

|---|---|

| Description | 3.3V ZERO DELAY CLOCK BUFFER |

| Manufacturer | Integrated Device |

| Size | 56.15 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| IDT2309A | Renesas | 3.3V ZERO DELAY CLOCK BUFFER |

| IDT2309NZ | Renesas | CLOCK BUFFER |

| IDT2309 | Renesas | 3.3V ZERO DELAY CLOCK BUFFER |

| IDT2305B | Renesas | 3.3V ZERO DELAY CLOCK BUFFER |

| IDT2305 | IDT | 3.3V ZERO DELAY CLOCK BUFFER |