IDT79R3052

Overview

- Instruction set compatible with IDT79R3000A and IDT79R3001 MIPS RISC CPUs

- High level of integration minimizes system cost, power consumption - IDT79R3000A /IDT79R3001 RISC Integer CPU - R3051 features 4KB of Instruction Cache - R3052 features 8KB of Instruction Cache - All devices feature 2kB of Data Cache - “E” Versions (Extended Architecture) feature full function Memory Management Unit, including 64entry Translation Lookaside Buffer (TLB) - 4-deep write buffer eliminates memory write stalls - 4-deep read buffer supports burst refill from slow memory devices * * * * *

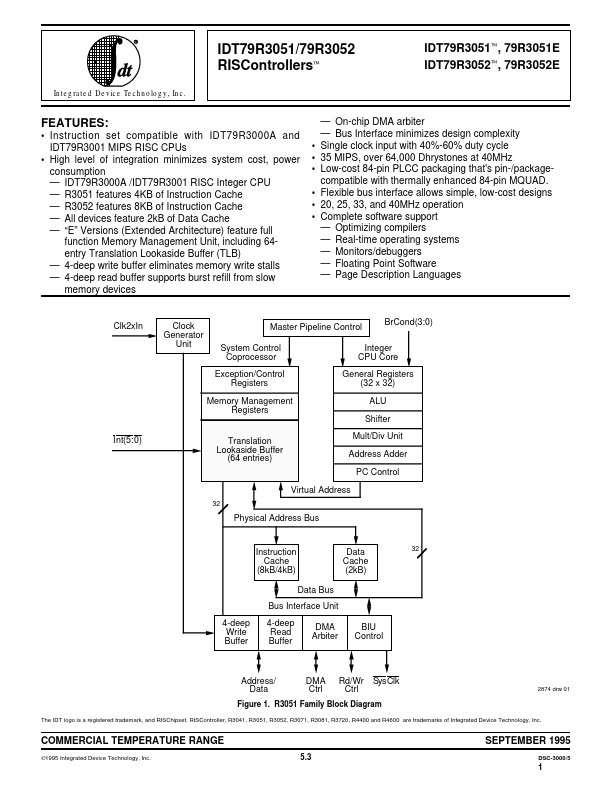

- - On-chip DMA arbiter - Bus Interface minimizes design complexity Single clock input with 40%-60% duty cycle 35 MIPS, over 64,000 Dhrystones at 40MHz Low-cost 84-pin PLCC packaging that's pin-/packagecompatible with thermally enhanced 84-pin MQUAD. Flexible bus interface allows simple, low-cost designs 20, 25, 33, and 40MHz operation Complete software support - Optimizing compilers - Real-time operating systems - Monitors/debuggers - Floating Point Software - Page Description Languages Clk2xIn Clock Generator Unit Master Pipeline Control System Control Coprocessor Exception/Control Registers Memory Management Registers BrCond(3:0) Integer CPU Core General Registers (32 x 32) ALU Shifter Int(5:0) Translation Lookaside Buffer (64 entries) Mult/Div Unit Address Adder PC Control Virtual Address 32 Physical Address Bus Instruction Cache (8kB/4kB) Data Bus Bus Interface Unit 4-deep Write Buffer 4-deep Read Buffer DMA Arbiter Data Cache (2kB) 32 BIU Control Address/ Data DMA Ctrl Rd/Wr Ctrl SysClk 2874 drw 01 Figure

- R3051 Family Block Diagram The IDT logo is a registered trademark, and RISChipset, RISController, R3041, R3051, R3052, R3071, R3081, R3720, R4400 and R4600 are trademarks of Integrated D