42S16100 Overview

Key Specifications

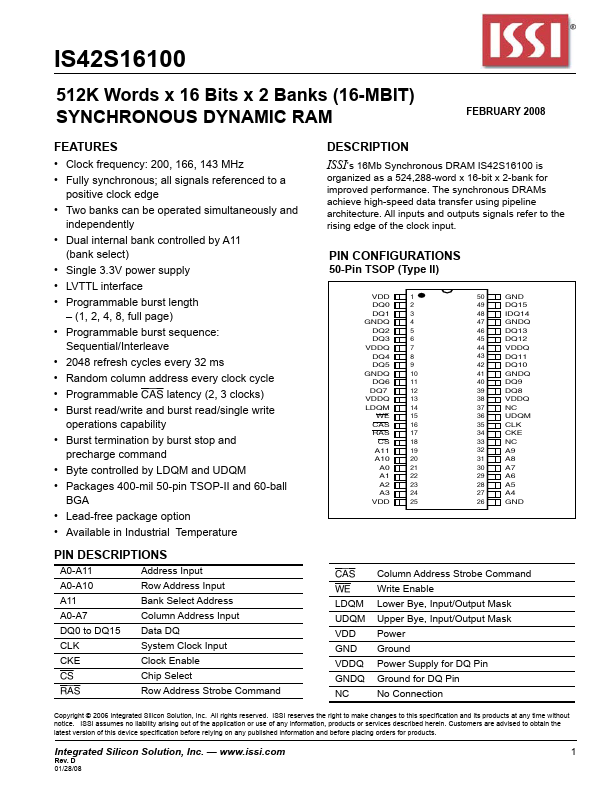

Package: TSOP

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Min Voltage (typical range): 3 V

Description

ISSI’s 16Mb Synchronous DRAM IS42S16100 is organized as a 524,288-word x 16-bit x 2-bank for improved performance. The synchronous DRAMs achieve high-speed data transfer using pipeline architecture.

Key Features

- Clock frequency: 200, 166, 143 MHz

- Fully synchronous; all signals referenced to a positive clock edge

- Two banks can be operated simultaneously and independently

- Dual internal bank controlled by A11 (bank select)

- Single 3.3V power supply