Datasheet Summary

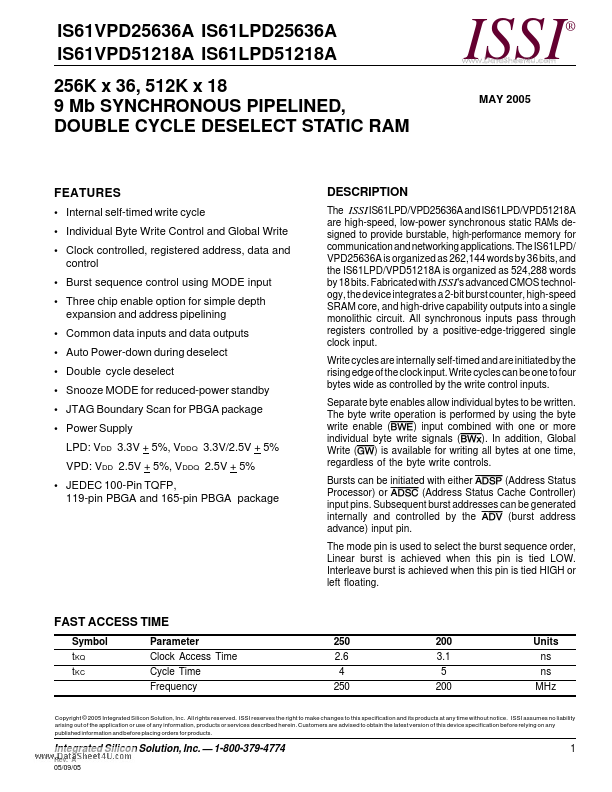

IS61VPD25636A IS61LPD25636A IS61VPD51218A IS61LPD51218A 256K x 36, 512K x 18 9 Mb SYNCHRONOUS PIPELINED, DOUBLE CYCLE DESELECT STATIC RAM

..

ISSI

MAY 2005

®

Features

- Internal self-timed write cycle

- Individual Byte Write Control and Global Write

- Clock controlled, registered address, data and control

- Burst sequence control using MODE input

- Three chip enable option for simple depth expansion and address pipelining

- mon data inputs and data outputs

- Auto Power-down during deselect

- Double cycle deselect

- Snooze MODE for reduced-power standby

- JTAG Boundary Scan for PBGA package

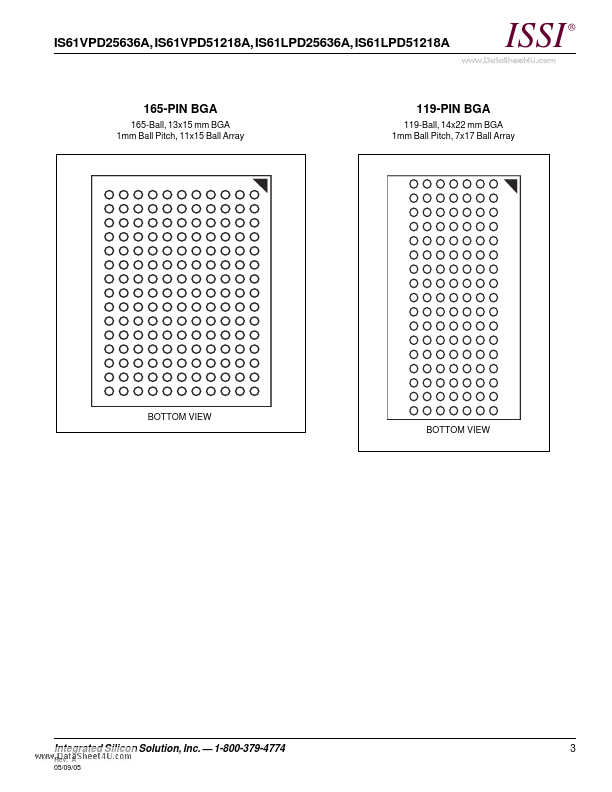

- Power Supply LPD: VDD 3.3V + 5%, VDDQ 3.3V/2.5V + 5% VPD: VDD 2.5V + 5%,...