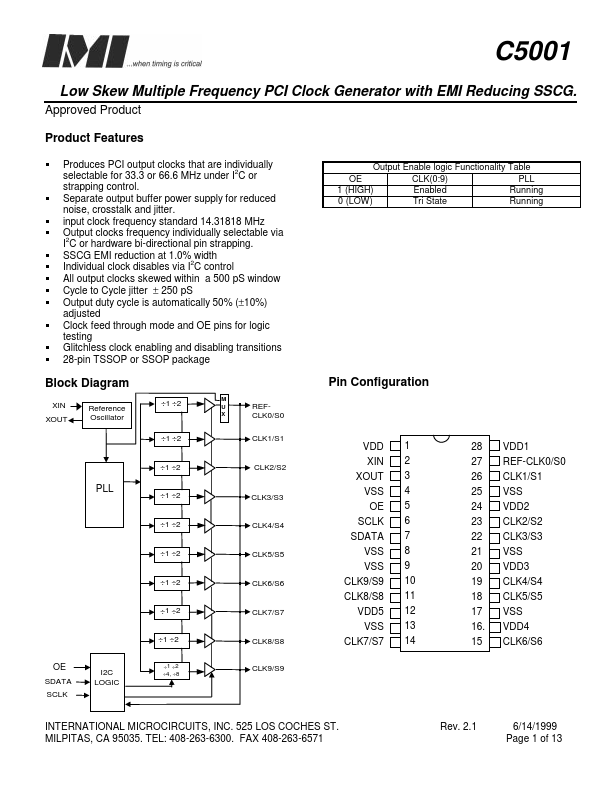

| Part | C5001 |

|---|---|

| Description | Low Skew Muliple Frequency PCI Clock Generator with EMI Reducing SSCG |

| Manufacturer | International |

| Size | 138.21 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| LEF-C5001T | Unknown Manufacturer | FULL COLOR LED LAMPS |

| LEF-C5002T | Letex | FULL COLOR LED LAMPS |