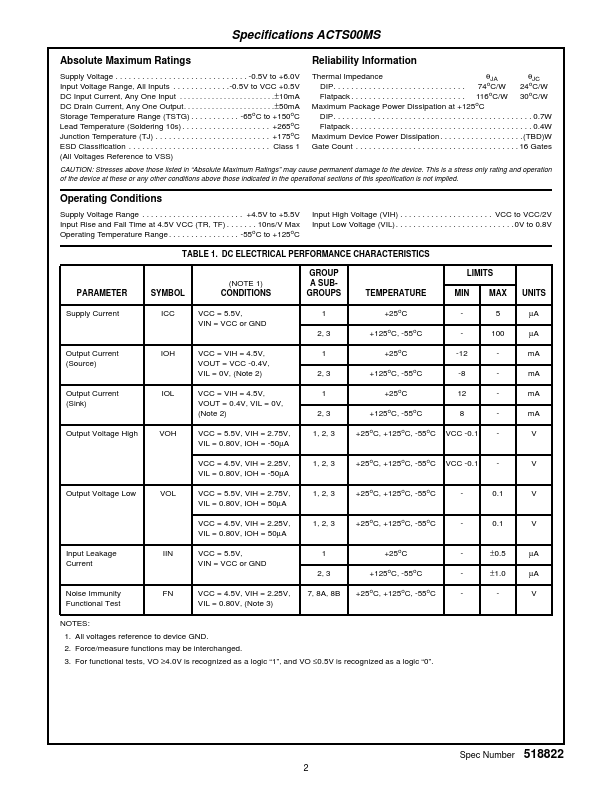

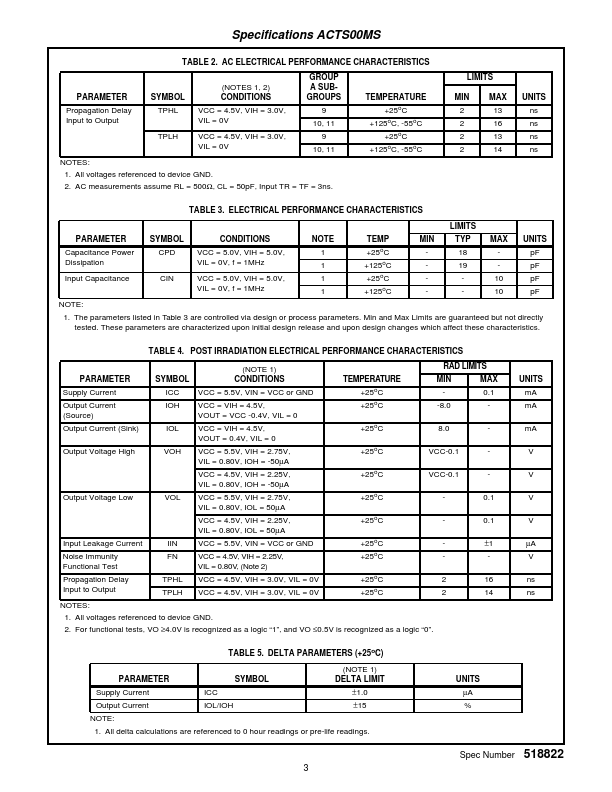

Datasheet Summary

April 1995

Radiation Hardened Quad 2-Input NAND Gate

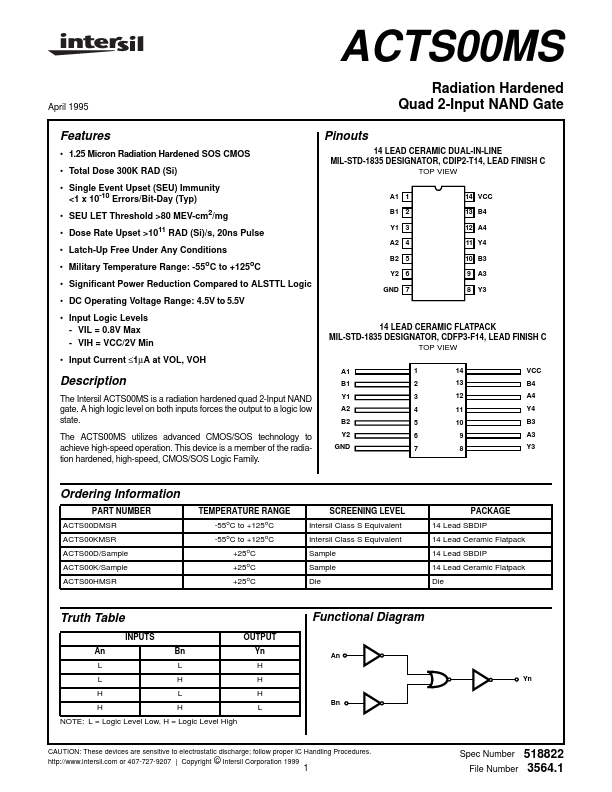

Pinouts

14 LEAD CERAMIC DUAL-IN-LINE MIL-STD-1835 DESIGNATOR, CDIP2-T14, LEAD FINISH C TOP VIEW

A1 1 B1 2 Y1 3 A2 4 B2 5 Y2 6 GND 7 14 VCC 13 B4 12 A4 11 Y4 10 B3 9 A3 8 Y3

Features

- 1.25 Micron Radiation Hardened SOS CMOS

- Total Dose 300K RAD (Si)

- Single Event Upset (SEU) Immunity <1 x 10-10 Errors/Bit-Day (Typ)

- SEU LET Threshold >80 MEV-cm2/mg

- Dose Rate Upset >1011 RAD (Si)/s, 20ns Pulse

- Latch-Up Free Under Any Conditions

- Military Temperature Range: -55oC to +125oC

- Significant Power Reduction pared to ALSTTL Logic

- DC Operating Voltage Range: 4.5V to 5.5V

- Input Logic Levels

- VIL = 0.8V Max

- VIH = VCC/2V...