CD4007UBMS

Overview

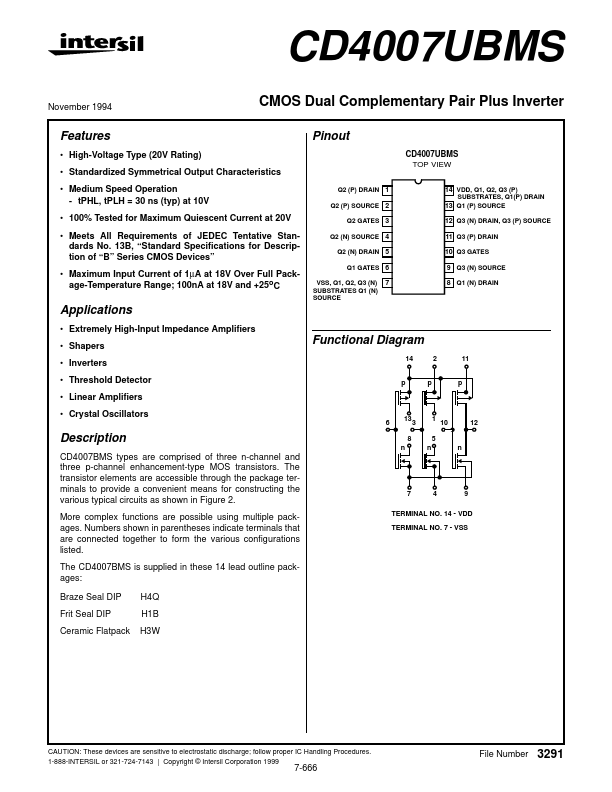

CD4007BMS types are comprised of three n-channel and three p-channel enhancement-type MOS transistors. The transistor elements are accessible through the package terminals to provide a convenient means for constructing the various typical circuits as shown in.

- High-Voltage Type (20V Rating)

- Standardized Symmetrical Output Characteristics

- Medium Speed Operation - tPHL, tPLH = 30 ns (typ) at 10V

- 100% Tested for Maximum Quiescent Current at 20V

- Meets All Requirements of JEDEC Tentative Standards No. 13B, “Standard Specifications for Description of “B” Series CMOS Devices”

- Maximum Input Current of 1µA at 18V Over Full Package-Temperature Range; 100nA at 18V and +25oC