CD40100BMS

Overview

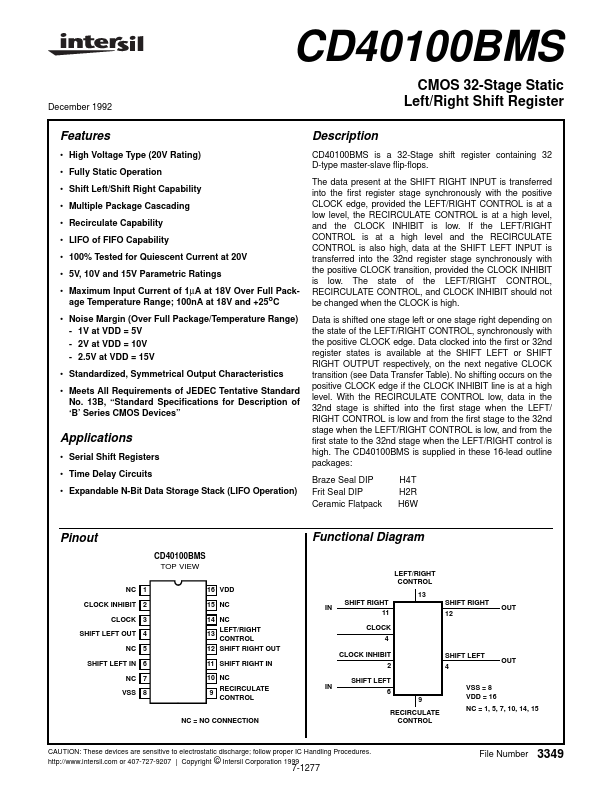

CD40100BMS is a 32-Stage shift register containing 32 D-type master-slave flip-flops. The data present at the SHIFT RIGHT INPUT is transferred into the first register stage synchronously with the positive CLOCK edge, provided the LEFT/RIGHT CONTROL is at a low level, the RECIRCULATE CONTROL is at a high level, and the CLOCK INHIBIT is low.

- High Voltage Type (20V Rating)

- Fully Static Operation

- Shift Left/Shift Right Capability

- Multiple Package Cascading

- Recirculate Capability

- LIFO of FIFO Capability

- 100% Tested for Quiescent Current at 20V

- 5V, 10V and 15V Parametric Ratings

- Maximum Input Current of 1µA at 18V Over Full Package Temperature Range; 100nA at 18V and