CDP1883C

Description

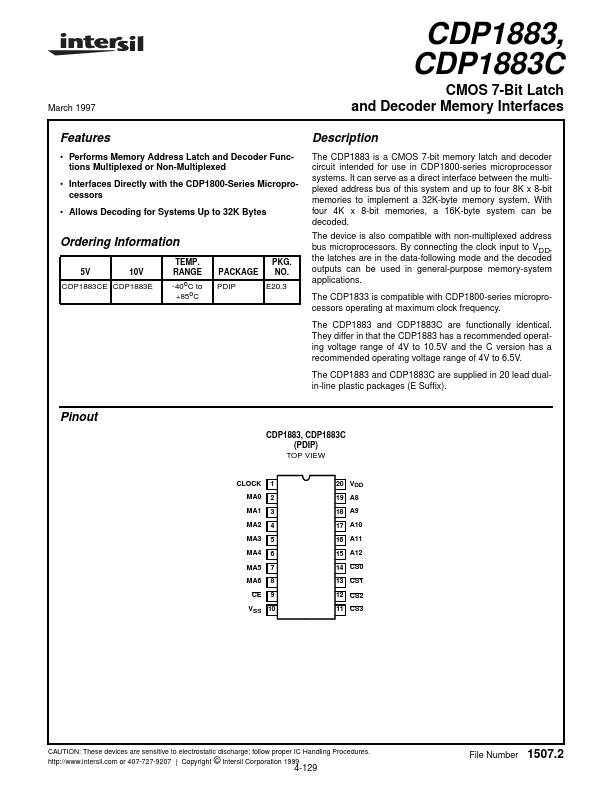

The CDP1883 is a CMOS 7-bit memory latch and decoder circuit intended for use in CDP1800-series microprocessor systems.

Key Features

- Performs Memory Address Latch and Decoder Functions Multiplexed or Non-Multiplexed

- Interfaces Directly with the CDP1800-Series Microprocessors

- Allows Decoding for Systems Up to 32K Bytes