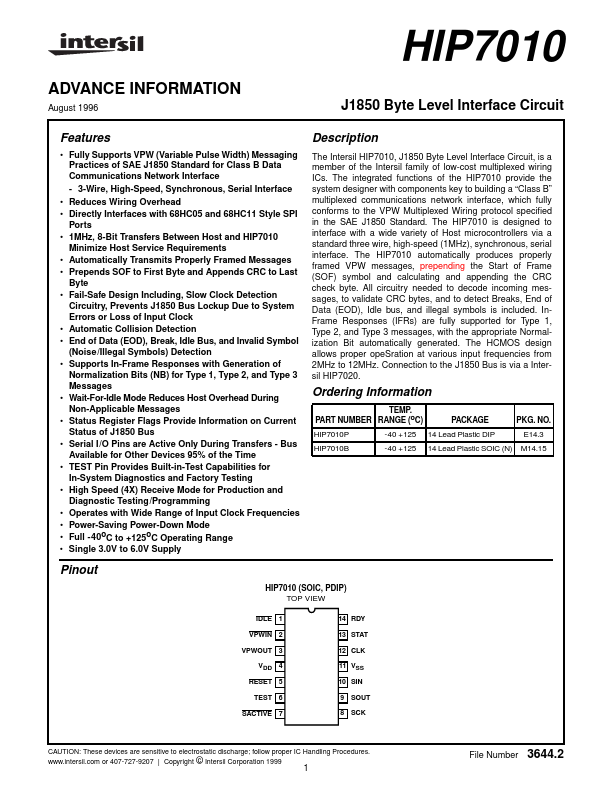

HIP7010 Description

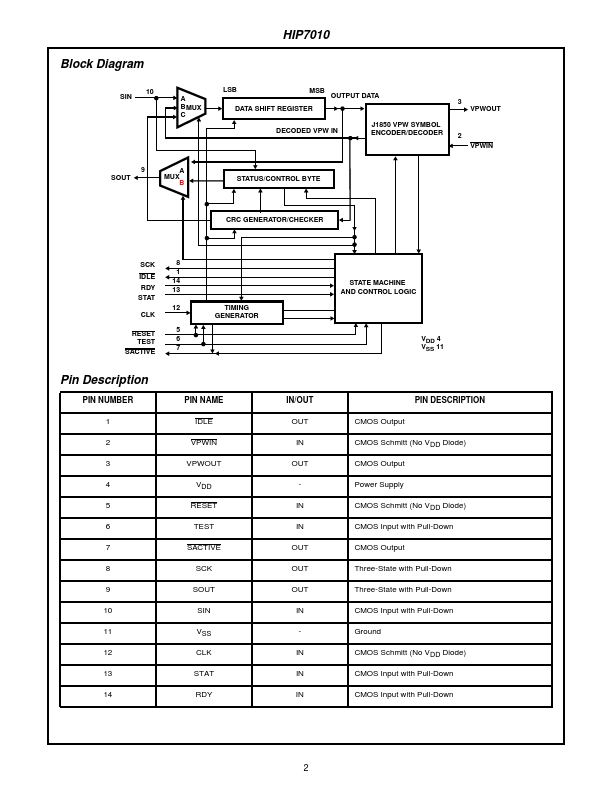

The Intersil HIP7010, J1850 Byte Level Interface Circuit, is a member of the Intersil family of low-cost multiplexed wiring ICs. The integrated functions of the HIP7010 provide the system designer with ponents key to building a “Class B” multiplexed munications network interface, which fully conforms to the VPW Multiplexed Wiring protocol specified in the SAE J1850 Standard. The HIP7010 is designed to interface with...

HIP7010 Key Features

- Fully Supports VPW (Variable Pulse Width) Messaging Practices of SAE J1850 Standard for Class B Data munications Network

- 3-Wire, High-Speed, Synchronous, Serial Interface

- Reduces Wiring Overhead

- Directly Interfaces with 68HC05 and 68HC11 Style SPI Ports

- 1MHz, 8-Bit Transfers Between Host and HIP7010 Minimize Host Service Requirements

- Automatically Transmits Properly Framed Messages

- Prepends SOF to First Byte and Appends CRC to Last Byte

- Fail-Safe Design Including, Slow Clock Detection Circuitry, Prevents J1850 Bus Lockup Due to System Errors or Loss of In

- Automatic Collision Detection

- End of Data (EOD), Break, Idle Bus, and Invalid Symbol (Noise/Illegal Symbols) Detection