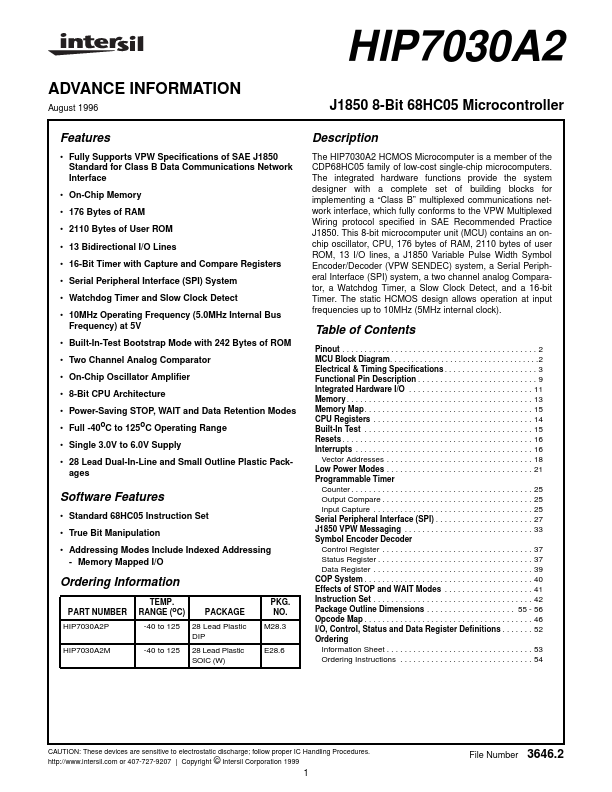

HIP7030A2

Description

The HIP7030A2 HCMOS Microputer is a member of the CDP68HC05 family of low-cost single-chip microputers. The integrated hardware functions provide the system designer with a plete set of building blocks for implementing a “Class B” multiplexed munications network interface, which fully conforms to the VPW Multiplexed Wiring protocol specified in SAE Remended Practice J1850. This 8-bit microputer unit (MCU) contains an onchip oscillator, CPU, 176 bytes of RAM, 2110 bytes of user ROM, 13 I/O lines, a J1850 Variable Pulse Width Symbol Encoder/Decoder (VPW SENDEC) system, a Serial Peripheral Interface (SPI) system, a two channel analog parator, a Watchdog Timer, a Slow Clock Detect, and a 16-bit Timer. The static HCMOS design allows operation at input frequencies up to 10MHz (5MHz internal clock).

Features

- Fully Supports VPW Specifications of SAE J1850 Standard for Class B Data munications Network Interface

- On-Chip Memory

- 176 Bytes of RAM

- 2110 Bytes of User ROM

- 13...