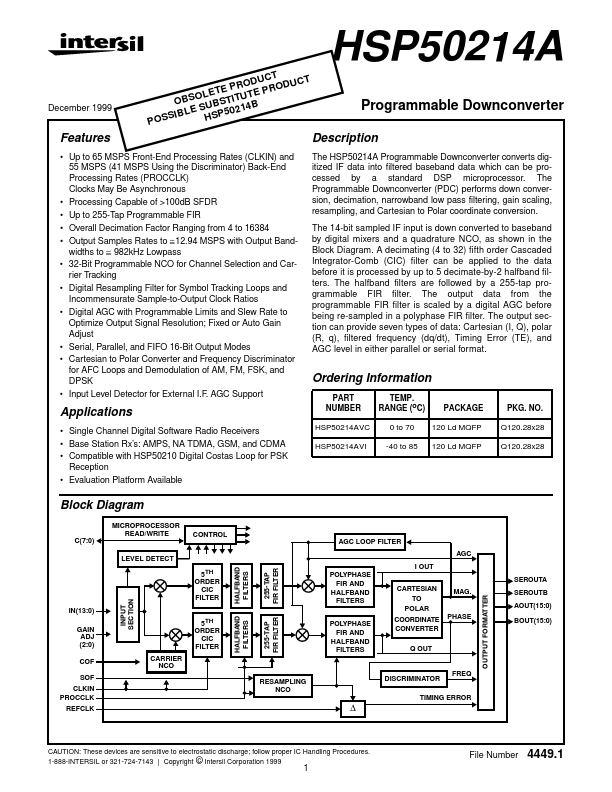

HSP50214A Key Features

- Up to 65 MSPS Front-End Processing Rates (CLKIN) and 55 MSPS (41 MSPS Using the Discriminator) Back-End Processing Rates

- Processing Capable of >100dB SFDR

- Up to 255-Tap Programmable FIR

- Overall Decimation Factor Ranging from 4 to 16384

- Output Samples Rates to ≅ 12.94 MSPS with Output Bandwidths to ≅ 982kHz Lowpass

- 32-Bit Programmable NCO for Channel Selection and Carrier Tracking

- Digital Resampling Filter for Symbol Tracking Loops and Inmensurate Sample-to-Output Clock Ratios

- Digital AGC with Programmable Limits and Slew Rate to Optimize Output Signal Resolution; Fixed or Auto Gain Adjust

- Serial, Parallel, and FIFO 16-Bit Output Modes

- Cartesian to Polar Converter and Frequency Discriminator for AFC Loops and Demodulation of AM, FM, FSK, and DPSK