KP85302

FEATURES

- Fully Operational up to 650V

- Peak Output Current 0.3A Source, 0.6A

Sink

- Integrated Fast Bootstrap Diode

- d V/dt Immunity of 50V/ns

- Logic Operational up to -7V on VS Pin

- Negative Voltage Tolerance on Inputs of

- 5V

- Independent UVLO for Both Channels

- Small Propagation Delay (175ns Typical)

- Delay Matching (15ns Typical)

- Dual Inputs with Output Interlock

- 3.3V, 5V and 15V Input Logic patible

- Schmitt Trigger Input with Hysteresis

- Maximum Supply Voltage of 20V

- Package Type: SOP-8

Applications

- Power MOSFET Driver

- Motor Drive, Appliances, Refrigerator

- Lighting, LED Power Supply

- Induction Heating

- DC-to-AC Inverters

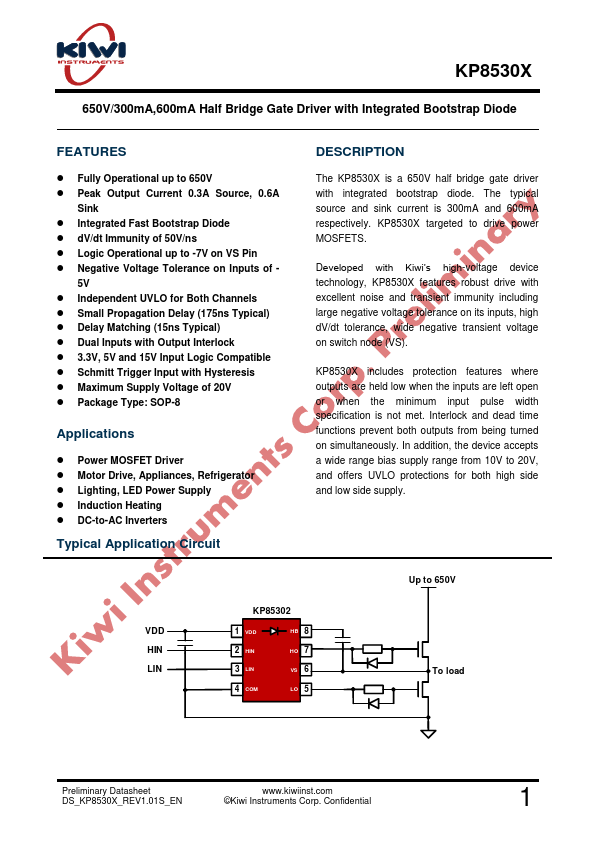

Typical Application Circuit

DESCRIPTION

The KP8530X is a 650V half bridge gate driver with integrated bootstrap diode. The typical source and sink current is 300m A and 600m A respectively. KP8530X targeted to drive power MOSFETS.

Developed with Kiwi’s high-voltage device technology, KP8530X features robust drive with excellent noise and...