LS7211

LS7211 is PROGRAMMABLE DIGITAL DELAY TIMER manufactured by LSI Computer Systems.

FEATURES

:

- 8-bit programmable delay from nanoseconds to days

- On chip oscillator (RC or Crystal) or external clock time base

- Selectable prescaler for real time delay generation based on 50Hz/60Hz time base or 32.768KHz watch crystal

- Four operating modes

- Reset input for delay abort

- Low quiescent and operating current

- Direct relay drive

- +4V to +18V operation (VDD-VSS)

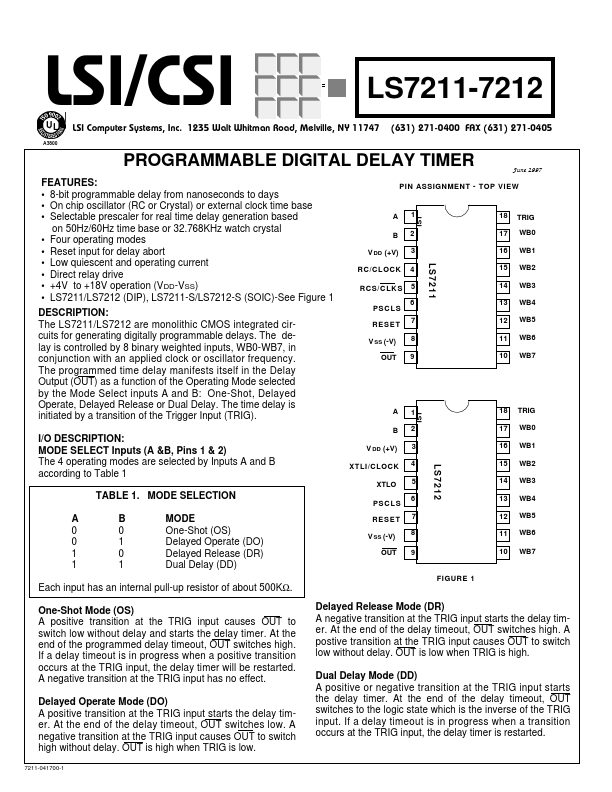

- LS7211/LS7212 (DIP), LS7211-S/LS7212-S (SOIC)-See Figure 1 DESCRIPTION

: The LS7211/LS7212 are monolithic CMOS integrated circuits for generating digitally programmable delays. The delay is controlled by 8 binary weighted inputs, WB0-WB7, in conjunction with an applied clock or oscillator frequency. The programmed time delay manifests itself in the Delay Output (OUT) as a function of the Operating Mode selected by the Mode Select inputs A and B: One-Shot, Delayed Operate, Delayed Release or Dual Delay. The time delay is initiated by a transition of the Trigger Input (TRIG). I/O DESCRIPTION

: MODE SELECT Inputs (A &B, Pins 1 & 2) The 4 operating modes are selected by Inputs A and B according to Table 1 TABLE 1. MODE SELECTION A 0 0 1 1 B 0 1 0 1 MODE One-Shot (OS) Delayed Operate (DO) Delayed Release (DR) Dual Delay (DD)

A B V DD (+V) RC/CLOCK RCS/CLKS PSCLS RESET V SS (-V) OUT 1 2 3 18 17 16

PIN ASSIGNMENT

- TOP VIEW

TRIG WB0 WB1 WB2 WB3 WB4 WB5 WB6 WB7

4 5 6 7 8 9

15 14 13 12 11 10

A B V DD (+V) XTLI/CLOCK XTLO PSCLS RESET V SS (-V) OUT

1 2

18 17 16 15 14 13 12 11 10

TRIG WB0 WB1 WB2 WB3 WB4 WB5 WB6 WB7

3 4 5 6 7 8 9

LS7212

FIGURE 1

Each input has an internal pull-up resistor of about 500KΩ. One-Shot Mode (OS) A positive transition at the TRIG input causes OUT to switch low without delay and starts the delay timer. At the end of the programmed delay timeout, OUT switches high. If a delay timeout is in progress when a positive transition occurs at the TRIG input, the delay timer will be restarted. A negative transition at the TRIG input has no effect. Delayed...