Datasheet Summary

ispLSI 3256E

®

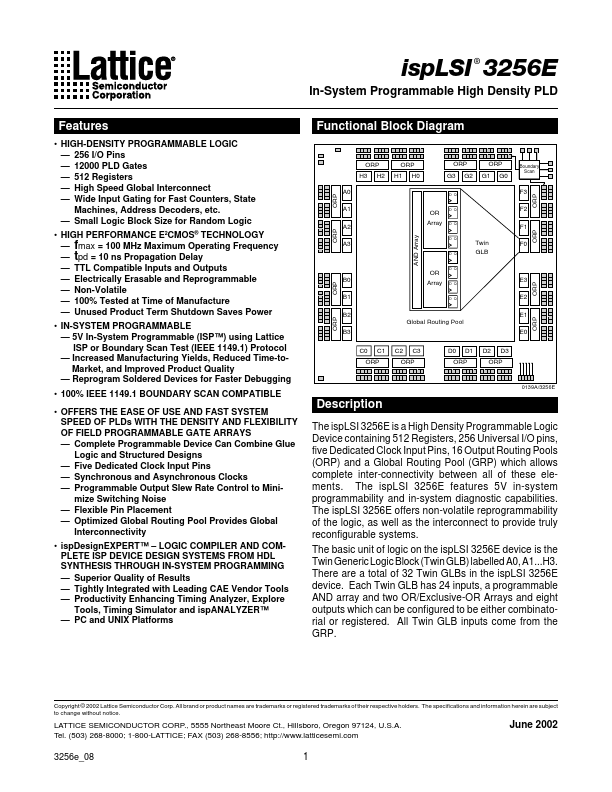

In-System Programmable High Density PLD Features

- HIGH-DENSITY PROGRAMMABLE LOGIC

- 256 I/O Pins

- 12000 PLD Gates

- 512 Registers

- High Speed Global Interconnect

- Wide Input Gating for Fast Counters, State Machines, Address Decoders, etc.

- Small Logic Block Size for Random Logic

- HIGH PERFORMANCE E2CMOS® TECHNOLOGY

- fmax = 100 MHz Maximum Operating Frequency

- tpd = 10 ns Propagation Delay

- TTL patible Inputs and Outputs

- Electrically Erasable and Reprogrammable

- Non-Volatile

- 100% Tested at Time of Manufacture

- Unused Product Term Shutdown Saves Power

- IN-SYSTEM PROGRAMMABLE

- 5V In-System Programmable (ISP™) using Lattice ISP or Boundary Scan Test (IEEE...