ISPGDXTMFAMILY

ISPGDXTMFAMILY is In-System Programmable Generic Digital CrosspointTM manufactured by Lattice Semiconductor.

isp GDX Family

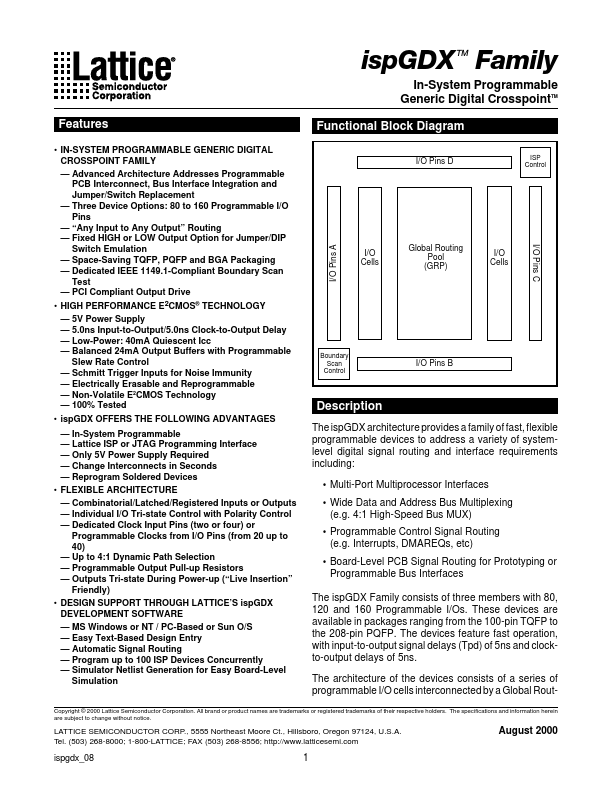

In-System Programmable Generic Digital Crosspoint Features

- IN-SYSTEM PROGRAMMABLE GENERIC DIGITAL CROSSPOINT FAMILY

- Advanced Architecture Addresses Programmable PCB Interconnect, Bus Interface Integration and Jumper/Switch Replacement

- Three Device Options: 80 to 160 Programmable I/O Pins

- “Any Input to Any Output” Routing

- Fixed HIGH or LOW Output Option for Jumper/DIP Switch Emulation

- Space-Saving TQFP, PQFP and BGA Packaging

- Dedicated IEEE 1149.1-pliant Boundary Scan Test

- PCI pliant Output Drive

- HIGH PERFORMANCE E2CMOS® TECHNOLOGY

- 5V Power Supply

- 5.0ns Input-to-Output/5.0ns Clock-to-Output Delay

- Low-Power: 40m A Quiescent Icc

- Balanced 24m A Output Buffers with Programmable Slew Rate Control

- Schmitt Trigger Inputs for Noise Immunity

- Electrically Erasable and Reprogrammable

- Non-Volatile E2CMOS Technology

- 100% Tested

- isp GDX OFFERS THE FOLLOWING ADVANTAGES

- In-System Programmable

- Lattice ISP or JTAG Programming Interface

- Only 5V Power Supply Required

- Change Interconnects in Seconds

- Reprogram Soldered Devices

- FLEXIBLE ARCHITECTURE

- binatorial/Latched/Registered Inputs or Outputs

- Individual I/O Tri-state Control with Polarity Control

- Dedicated Clock Input Pins (two or four) or Programmable Clocks from I/O Pins (from 20 up to 40)

- Up to 4:1 Dynamic Path...