ISPLSI2064A

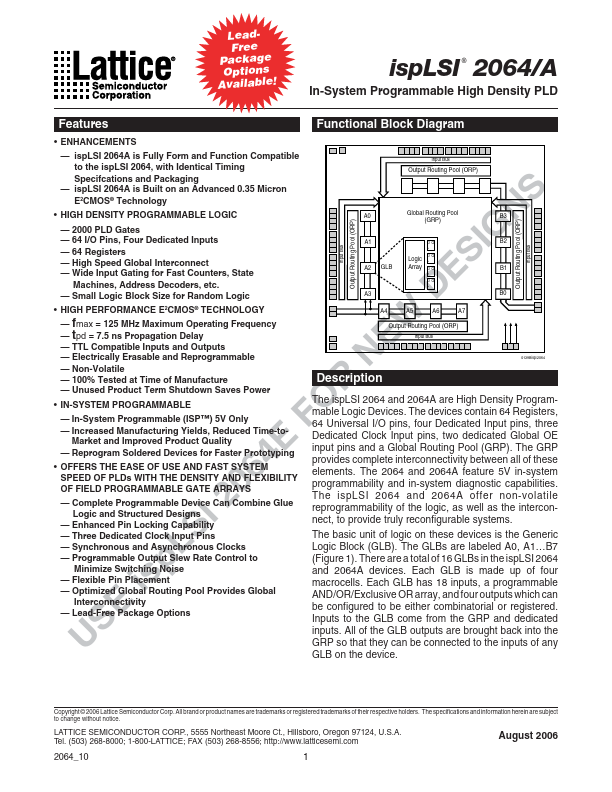

ISPLSI2064A is In-System Programmable High Density PLD manufactured by Lattice Semiconductor.

- Part of the ISPLSI2064 comparator family.

- Part of the ISPLSI2064 comparator family.

LeadFree Package Options Available! ispLSI® 2064/A

In-System Programmable High Density PLD

USE ispLSI 2064E FOR NEW

Features

- ENHANCEMENTS

- ispLSI 2064A is Fully Form and Function patible to the ispLSI 2064, with Identical Timing Specifcations and Packaging

- ispLSI 2064A is Built on an Advanced 0.35 Micron E2CMOS® Technology

- HIGH DENSITY PROGRAMMABLE LOGIC

- 2000 PLD Gates

- 64 I/O Pins, Four Dedicated Inputs

- 64 Registers

- High Speed Global Interconnect

- Wide Input Gating for Fast Counters, State

Machines, Address Decoders, etc.

- Small Logic Block Size for Random Logic

- HIGH PERFORMANCE E2CMOS® TECHNOLOGY

- fmax = 125 MHz Maximum Operating Frequency

- tpd = 7.5 ns...