ispLSI2064E

ispLSI2064E is In-System Programmable SuperFAST High Density PLD manufactured by Lattice Semiconductor.

- Part of the ispLSI2064E-100LT100 comparator family.

- Part of the ispLSI2064E-100LT100 comparator family.

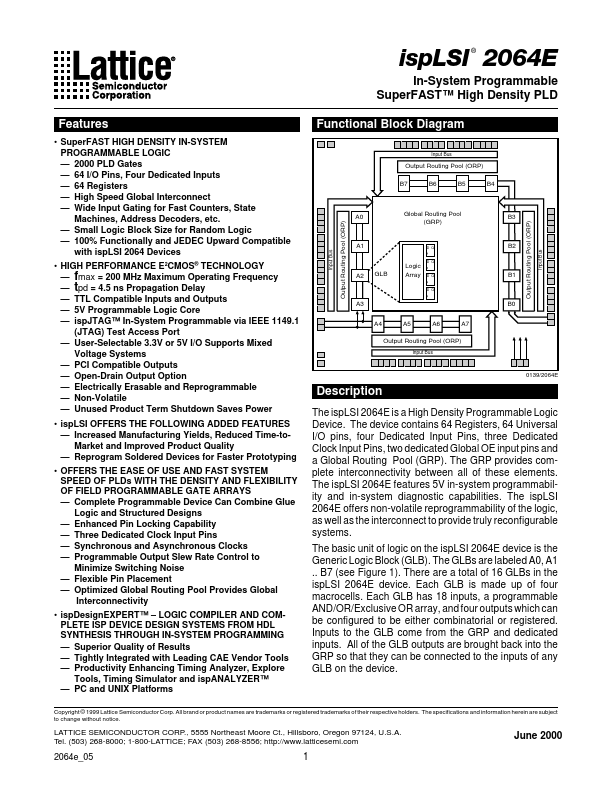

ispLSI® 2064E

In-System Programmable SuperFAST™ High Density PLD

Features

- SuperFAST HIGH DENSITY IN-SYSTEM PROGRAMMABLE LOGIC

- 2000 PLD Gates

- 64 I/O Pins, Four Dedicated Inputs

- 64 Registers

- High Speed Global Interconnect

- Wide Input Gating for Fast Counters, State Machines, Address Decoders, etc.

- Small Logic Block Size for Random Logic

- 100% Functionally and JEDEC Upward patible with ispLSI 2064 Devices

- HIGH PERFORMANCE E2CMOS® TECHNOLOGY

- fmax = 200 MHz Maximum Operating Frequency

- tpd = 4.5 ns Propagation Delay

- TTL patible Inputs and Outputs

- 5V Programmable Logic Core

- ispJTAG™ In-System Programmable via IEEE 1149.1

(JTAG) Test Access Port

- User-Selectable...