Datasheet Summary

.. ispLSI 5256VE

®

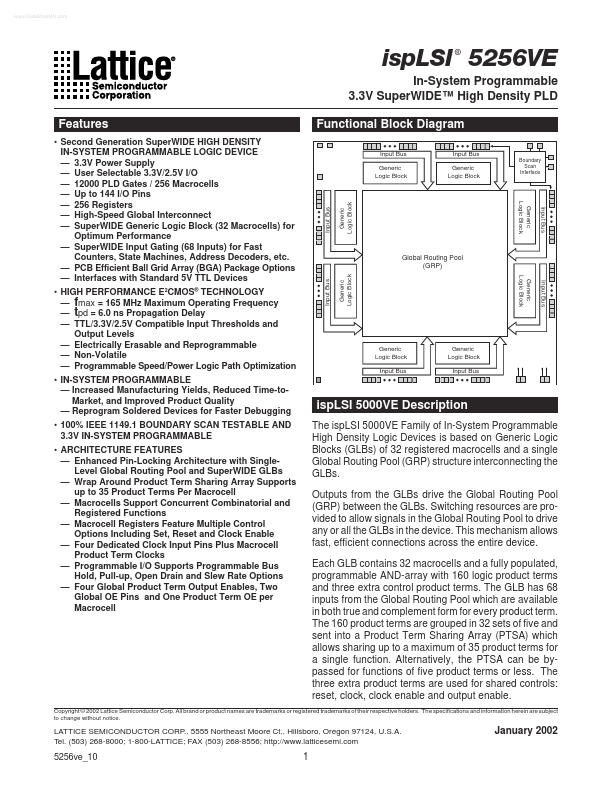

In-System Programmable 3.3V SuperWIDE™ High Density PLD Features

- Second Generation SuperWIDE HIGH DENSITY IN-SYSTEM PROGRAMMABLE LOGIC DEVICE

- 3.3V Power Supply

- User Selectable 3.3V/2.5V I/O

- 12000 PLD Gates / 256 Macrocells

- Up to 144 I/O Pins

- 256 Registers

- High-Speed Global Interconnect

- SuperWIDE Generic Logic Block (32 Macrocells) for Optimum Performance

- SuperWIDE Input Gating (68 Inputs) for Fast Counters, State Machines, Address Decoders, etc.

- PCB Efficient Ball Grid Array (BGA) Package Options

- Interfaces with Standard 5V TTL Devices

- HIGH PERFORMANCE E2CMOS® TECHNOLOGY

- fmax = 165 MHz Maximum Operating Frequency

- tpd = 6.0...