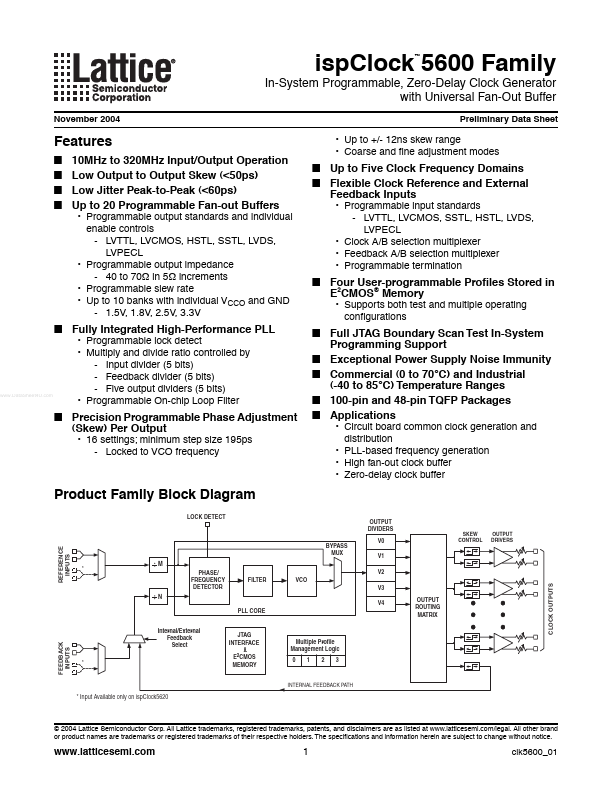

Datasheet Summary

ispClock 5600 Family

™

In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer

November 2004 Preliminary Data Sheet

Features

- -

- - 10MHz to 320MHz Input/Output Operation Low Output to Output Skew (<50ps) Low Jitter Peak-to-Peak (<60ps) Up to 20 Programmable Fan-out Buffers

- Programmable output standards and individual enable controls

- LVTTL, LVCMOS, HSTL, SSTL, LVDS, LVPECL

- Programmable output impedance

- 40 to 70Ω in 5Ω increments

- Programmable slew rate

- Up to 10 banks with individual VCCO and GND

- 1.5V, 1.8V, 2.5V, 3.3V

- Programmable lock detect

- Multiply and divide ratio controlled by

- Input divider (5 bits)

- Feedback divider (5 bits)

- Five...