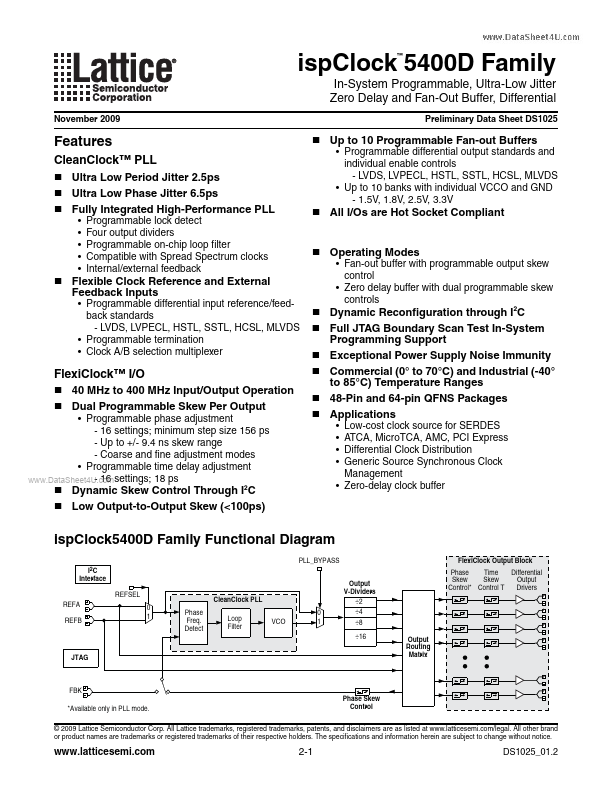

ispClock5406D Overview

Key Features

- Ultra Low Period Jitter 2.5ps

- Ultra Low Phase Jitter 6.5ps

- Fully Integrated High-Performance PLL

- Up to 10 Programmable Fan-out Buffers

- Programmable differential output standards and individual enable controls

- LVDS, LVPECL, HSTL, SSTL, HCSL, MLVDS

- Up to 10 banks with individual VCCO and GND

- 1.5V, 1.8V, 2.5V, 3.3V

- All I/Os are Hot Socket Compliant

- Operating Modes