ispClock5410D

ispClock5410D is Zero Delay And Fan-Out Buffer manufactured by Lattice Semiconductor.

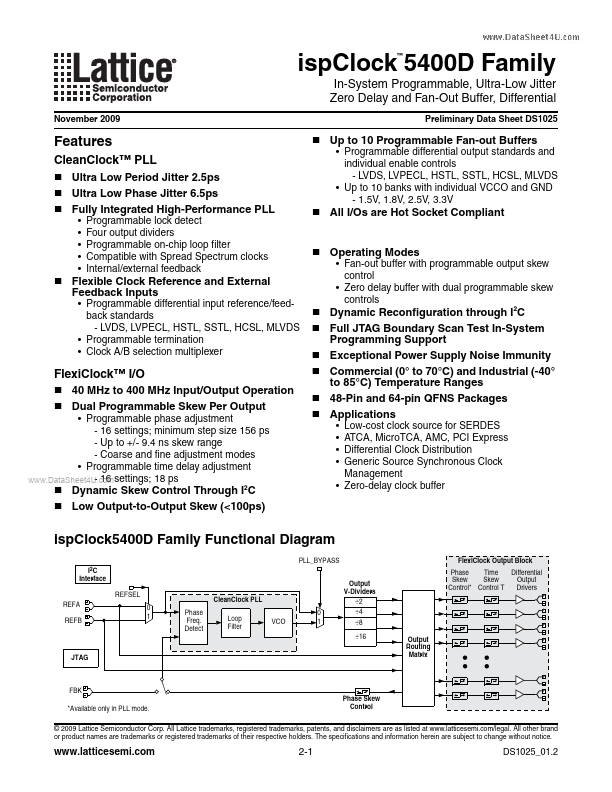

ispClock 5400D Family

™

In-System Programmable, Ultra-Low Jitter Zero Delay and Fan-Out Buffer, Differential

November 2009 Preliminary Data Sheet DS1025

Features

CleanClock™ PLL

- Ultra Low Period Jitter 2.5ps

- Ultra Low Phase Jitter 6.5ps

- Fully Integrated High-Performance PLL

- -

- -

- Programmable lock detect Four output dividers Programmable on-chip loop filter patible with Spread Spectrum clocks Internal/external feedback

- Up to 10 Programmable Fan-out Buffers

- Programmable differential output standards and individual enable controls

- LVDS, LVPECL, HSTL, SSTL, HCSL, MLVDS

- Up to 10 banks with individual VCCO and GND

- 1.5V, 1.8V, 2.5V, 3.3V

- All I/Os are Hot Socket...