OR2C15A

OR2C15A is manufactured by Lattice.

Data Sheet October 2003

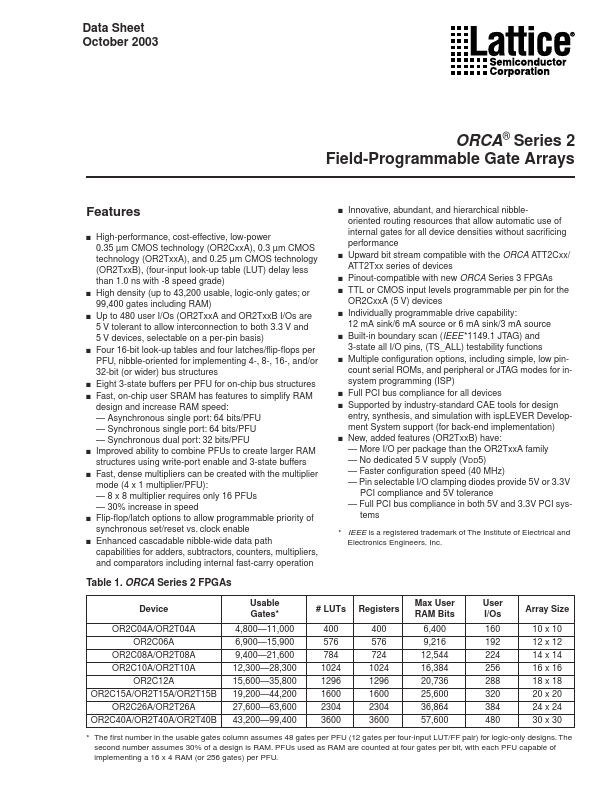

ORCA® Series 2 Field-Programmable Gate Arrays

Features

- -

- -

- -

- -

- -

- High-performance, cost-effective, low-power 0.35 µm CMOS technology (OR2CxxA), 0.3 µm CMOS technology (OR2TxxA), and 0.25 µm CMOS technology (OR2TxxB), (four-input look-up table (LUT) delay less than 1.0 ns with -8 speed grade) High density (up to 43,200 usable, logic-only gates; or 99,400 gates including RAM) Up to 480 user I/Os (OR2TxxA and OR2TxxB I/Os are 5 V tolerant to allow interconnection to both 3.3 V and 5 V devices, selectable on a per-pin basis) Four 16-bit look-up tables and four latches/flip-flops per PFU, nibble-oriented for implementing 4-, 8-, 16-, and/or 32-bit...