LY622568 Overview

Description

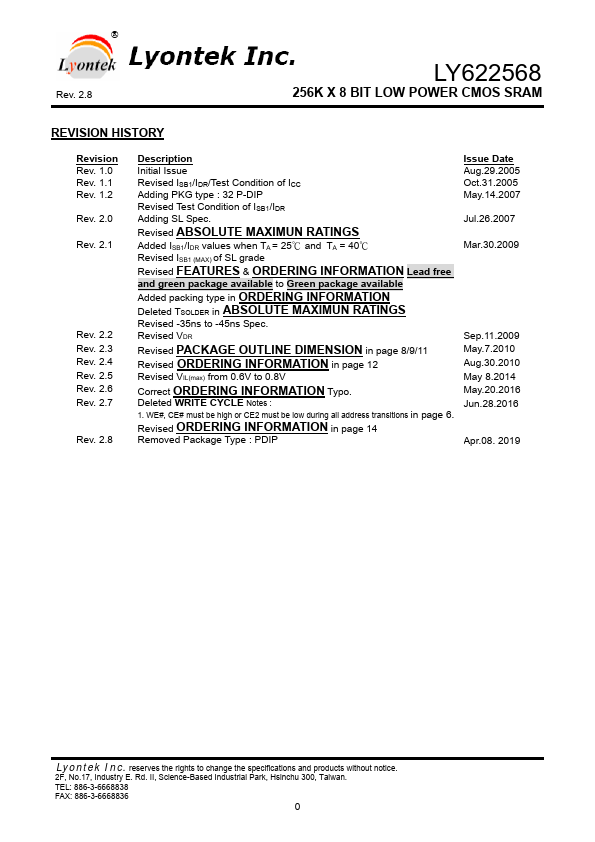

Initial Issue Revised ISB1/IDR/Test Condition of ICC Adding PKG type : 32 P-DIP Revised Test Condition of ISB1/IDR Adding SL Spec. Revised ABSOLUTE MAXIMUN RATINGS Added ISB1/IDR values when TA = 25℃ and TA = 40℃ Revised ISB1 (MAX) of SL grade Revised FEATURES & and green package available to Green package available Added packing type in Revised -35ns to -45ns Spec.

Key Features

- Fast access time : 45/55/70ns

- Low power consumption: Operating current : 50/40/30mA (TYP.) Standby current : 3A@5V(TYP.) LL/SL version 2A@3V(TYP.) SL version

- Single 4.5V ~ 5.5V power supply

- All inputs and outputs TTL compatible

- Fully static operation

- Tri-state output

- Data retention voltage : 1.5V (MIN.)

- Green package available

- Package : 32-pin 450 mil SOP 32-pin 8mm x 20mm TSOP I 32-pin 8mm x 13.4mm sTSOP