Datasheet Summary

CHD408LVS-55,70 CHD408LVW-55,70

Rev 2.2 Jul’03

4M -BIT (512K-WORD BY 8-BIT) SuperT-SRAM™ LOW-POWER ASYNCHRONOUS SRAM

DESCRIPTION

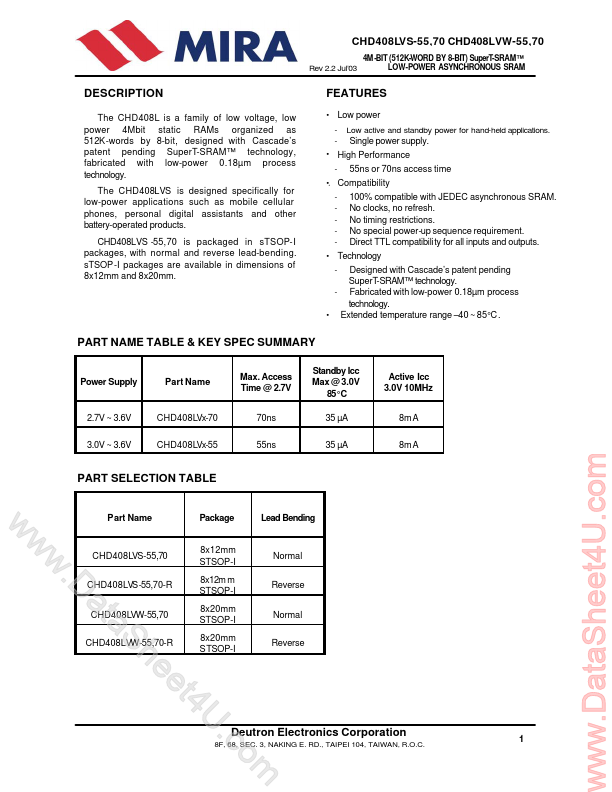

The CHD408L is a family of low voltage, low power 4Mbit static RAMs organized as 512K-words by 8-bit, designed with Cascade’s patent pending SuperT-SRAM™ technology, fabricated with low-power 0.18µm process technology. The CHD408LVS is designed specifically for low-power applications such as mobile cellular phones, personal digital assistants and other battery-operated products. CHD408LVS -55,70 is packaged in sTSOP-I packages, with normal and reverse lead-bending. sTSOP-I packages are available in dimensions of 8x12mm and 8x20mm.

Features

- Low power Low...