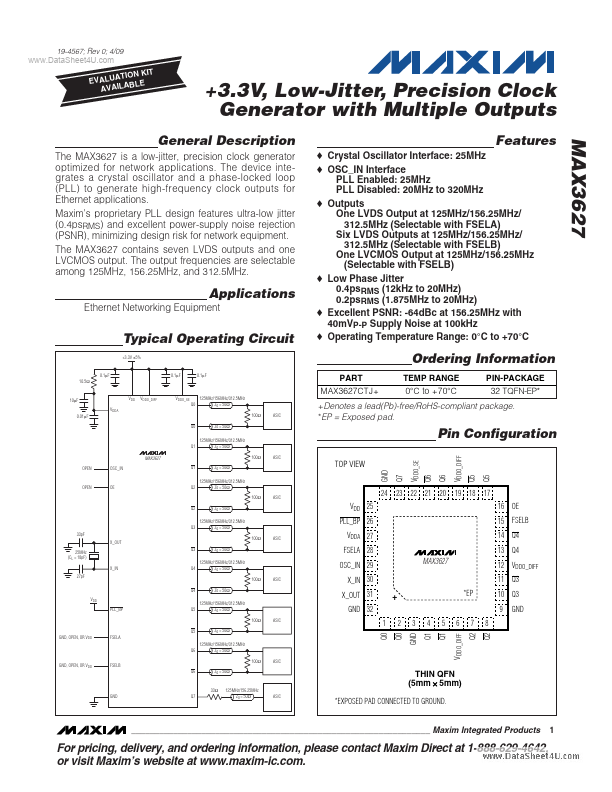

| Part | MAX3627 |

|---|---|

| Description | Precision Clock Generator |

| Manufacturer | Maxim Integrated |

| Size | 647.41 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| MAX3622 | Microsemi | Precision Clock Generator |

| MAX362 | Maxim Integrated | Precision / Quad / SPST Analog Switches |