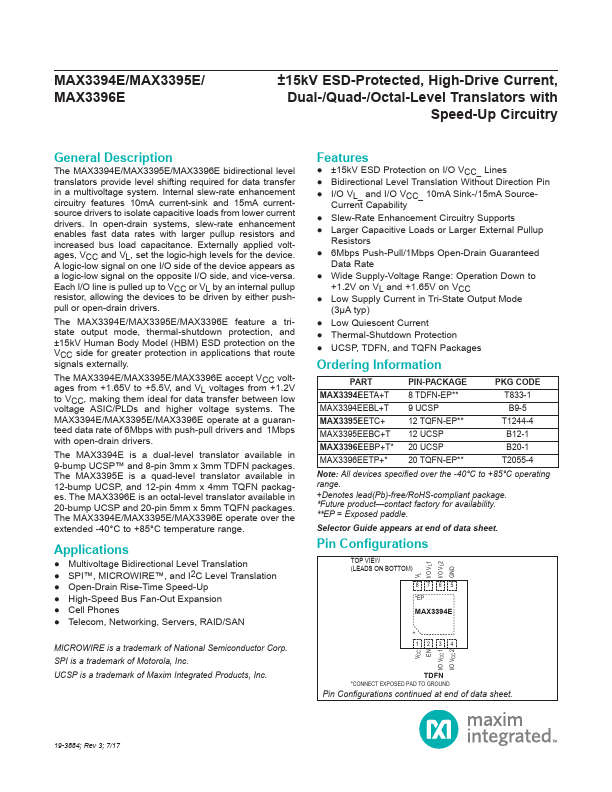

MAX3396E

Description

The MAX3394E/MAX3395E/MAX3396E bidirectional level translators provide level shifting required for data transfer in a multivoltage system.

Key Features

- 10mA current-sink and 15mA currentsource drivers to isolate capacitive loads from lower current drivers

- In open-drain systems, slew-rate enhancement enables fast data rates with larger pullup resistors and increased bus load capacitance

- Externally applied voltages, VCC and VL, set the logic-high levels for the device

- A logic-low signal on one I/O side of the device appears as a logic-low signal on the opposite I/O side, and vice-versa

- The MAX3394E/MAX3395E/MAX3396E feature a tristate output mode, therm