MAX9125

Key Features

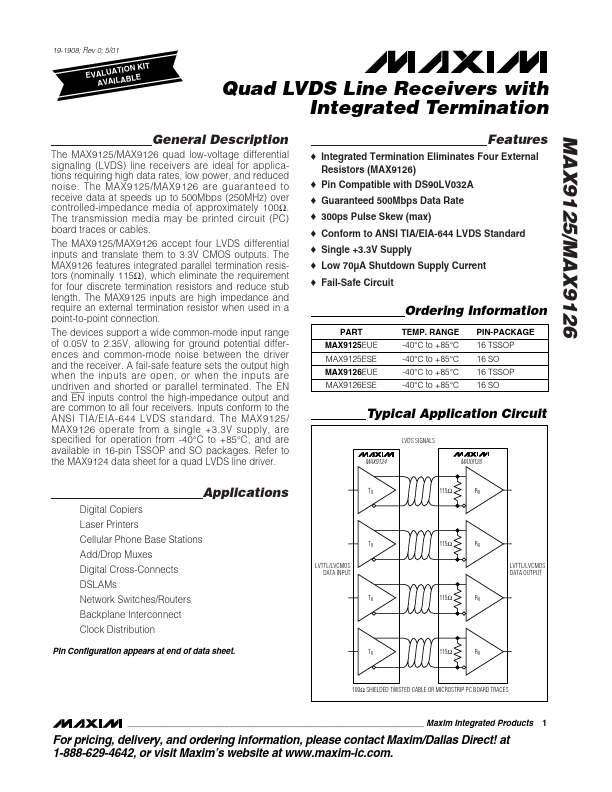

- The MAX9125/MAX9126 are guaranteed to receive data at speeds up to 500Mbps (250MHz) over controlled-impedance media of approximately 100Ω

- The transmission media may be printed circuit (PC) board traces or cables

- The MAX9125/MAX9126 accept four LVDS differential inputs and translate them to 3.3V CMOS outputs

- The MAX9125 inputs are high impedance and require an external termination resistor when used in a point-to-point connection

- A fail-safe feature sets the output high when the inputs are open, or when the inputs are undriven and shorted or parallel terminated

- The EN and EN inputs control the high-impedance output and are mon to all four receivers

- Inputs conform to the ANSI TIA/EIA-644 LVDS standard

- Refer to the MAX9124 data sheet for a quad LVDS line driver