KSZ8862-16MQL Overview

Key Specifications

Package: PQFP

Mount Type: Surface Mount

Pins: 128

Operating Voltage: 3.3 V

Description

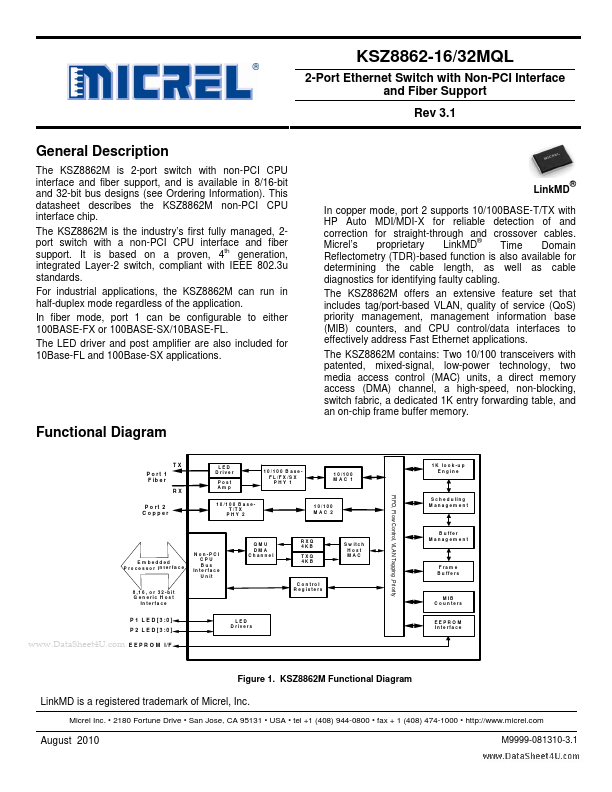

The KSZ8862M is 2-port switch with non-PCI CPU interface and fiber support, and is available in 8/16-bit and 32-bit bus designs (see ® In copper mode, port 2 supports 10/100BASE-T/TX with HP Auto MDI/MDI-X for reliable detection of and correction for straight-through and crossover cables. ® Micrel’s proprietary LinkMD Time Domain Reflectometry (TDR)-based function is also available for determining the cable length, as well as cable diagnostics for identifying faulty cabling.