MIC5167 Overview

Description

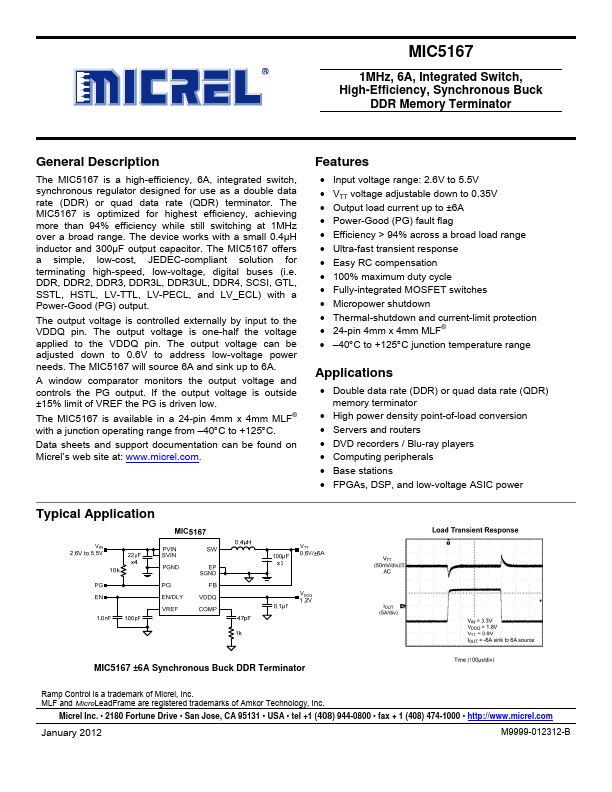

The MIC5167 is a high-efficiency, 6A, integrated switch, synchronous regulator designed for use as a double data rate (DDR) or quad data rate (QDR) terminator. The MIC5167 is optimized for highest efficiency, achieving more than 94% efficiency while still switching at 1MHz over a broad range.