SY100EP196V Overview

Description

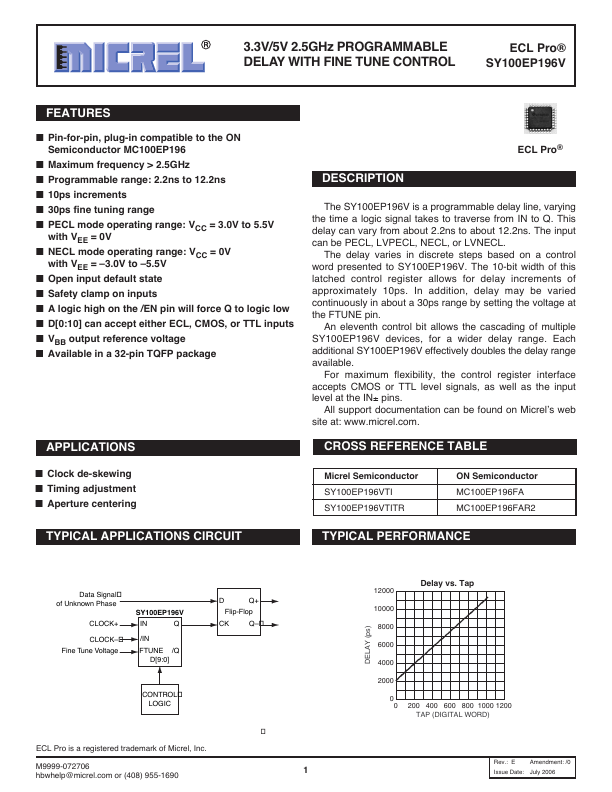

The SY100EP196V is a programmable delay line, varying the time a logic signal takes to traverse from IN to Q. This delay can vary from about 2.2ns to about 12.2ns.

Key Features

- Pin-for-pin, plug-in compatible to the ON Semiconductor MC100EP196

- Maximum frequency > 2.5GHz

- Programmable range: 2.2ns to 12.2ns

- 10ps increments

- 30ps fine tuning range

- PECL mode operating range: VCC = 3.0V to 5.5V with VEE = 0V

- NECL mode operating range: VCC = 0V with VEE = –3.0V to –5.5V

- Open input default state

- Safety clamp on inputs

- A logic high on the /EN pin will force Q to logic low