SY100H607

SY100H607 is REGISTERED HEX PECL-TO-TTL manufactured by Micrel Semiconductor.

- Part of the SY10H607 comparator family.

- Part of the SY10H607 comparator family.

Micrel, Inc.

NOT REMENDED FOR NEW DESIGNS

REGISTERED HEX PECL-TO-TTL

SY10H607

SY1S0YH10600H7607

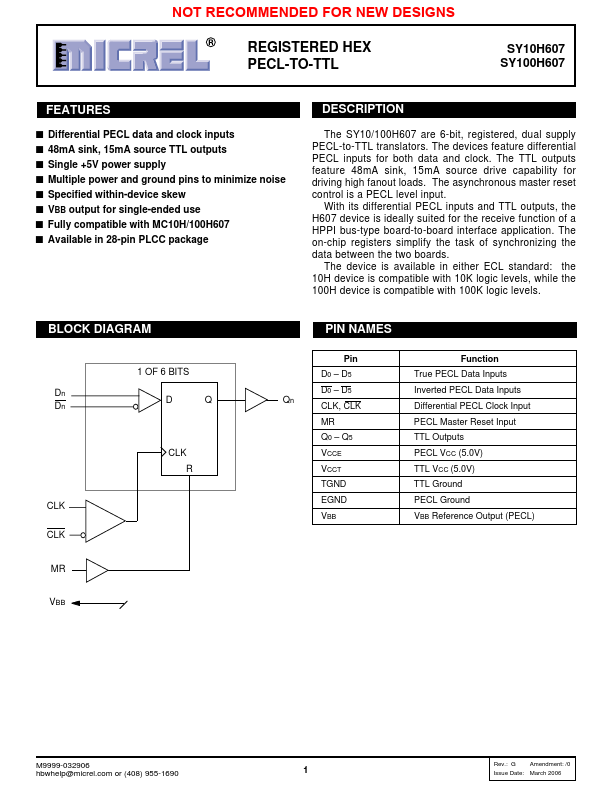

Features s Differential PECL data and clock inputs s 48m A sink, 15m A source TTL outputs s Single +5V power supply s Multiple power and ground pins to minimize noise s Specified within-device skew s VBB output for single-ended use s Fully patible with MC10H/100H607 s Available in 28-pin PLCC package

DESCRIPTION

The SY10/100H607 are 6-bit, registered, dual supply PECL-to-TTL translators. The devices feature differential PECL inputs for both data and clock. The TTL outputs feature 48m A sink, 15m A source drive capability for driving high fanout loads. The asynchronous master reset control is a PECL level input.

With its differential PECL inputs and TTL outputs, the H607 device is ideally suited for the receive function of a HPPI bus-type board-to-board interface application. The on-chip registers simplify the task of synchronizing the data between the two boards.

The device is available in either ECL standard: the 10H device is patible with 10K logic levels, while the 100H device is patible with 100K logic levels.

BLOCK DIAGRAM

1 OF 6 BITS Dn

DQ Dn

CLK CLK MR VBB

CLK R

PIN NAMES

Pin D0

- D5 D0

- D5 Qn CLK, CLK MR Q0

- Q5 VCCE VCCT TGND EGND VBB

Function True PECL Data Inputs Inverted PECL Data Inputs Differential PECL Clock Input PECL Master Reset Input TTL Outputs PECL VCC (5.0V) TTL VCC (5.0V) TTL Ground PECL Ground VBB Reference Output (PECL)

M9999-032906 hbwhelp@micrel. or (408) 955-1690

Rev.: G Amendment: /0 Issue Date: March 2006

Micrel, Inc.

SY10H607 SY100H607

PACKAGE/ORDERING INFORMATION

Q2 Q1 Q0 TGND CLK CLK VBB

D0 D0 EGND D1 D1 D2 D2

Q3 VCCT Q4 TGND Q5 VCCT MR

25 24 23 22 21 20 19 26 18 27 17 28...