SY10EL32V

SY10EL32V is 5V/3.3V / 2 DIVIDER manufactured by Micrel Semiconductor.

- Part of the SY100EL32V comparator family.

- Part of the SY100EL32V comparator family.

5V/3.3V ÷ 2 DIVIDER

Clock Works™ SY10EL32V SY100EL32V

Features s s s s s s 3.3V and 5V power supply options 510ps propagation delay 3.0GHz toggle frequency High bandwidth output transistions Internal 75KΩ input pull-down resistors Available in 8-pin SOIC package

DESCRIPTION

The SY10/100EL32V are integrated ÷ 2 dividers. The differential clock inputs and the VBB allow a differential, single-ended or AC-coupled interface to the device. If used, the VBB output should be bypassed to ground with a 0.01µF capacitor. Also note that the VBB is designed to be used as an input bias on the EL32V only; the VBB output has limited current sink and source capability. The reset pin is asynchronous and is asserted on the rising edge. Upon power-on, the internal flip-flop will attain a random state; the reset allows for the synchronization of multiple EL32Vs in a system.

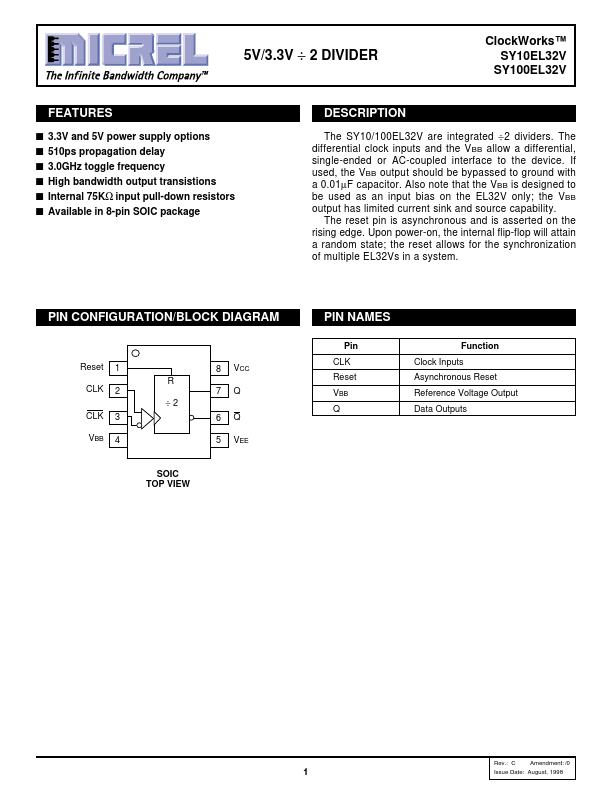

PIN CONFIGURATION/BLOCK DIAGRAM

PIN NAMES

Pin Function Clock Inputs Asynchronous Reset Reference Voltage Output Data Outputs

Reset CLK CLK VBB

1 R 2 ÷2 3 4

8 7 6 5

VCC Q Q VEE

CLK Reset VBB Q

SOIC TOP VIEW

Rev.: C

Amendment: /0

Issue Date: August, 1998

Micrel

Clock Works™ SY10EL32V SY100EL32V

DC ELECTRICAL CHARACTERISTICS(1)

VEE = VEE (Min.) to VEE (Max.); VCC = GND

TA =

- 40°C Symbol IEE Parameter Power Supply Current 10EL 100EL Min.

- - Typ. 25 25

- -

- Max. 30 30 Min.

- - TA = 0°C Typ. 25 25

- -

- Max. 30 30 TA = +25°C Min.

- - Typ. 25...