SY54011R

SY54011R is Low Voltage 1.2V/1.8V CML 1:2 Fanout Buffer manufactured by Micrel Semiconductor.

.Data Sheet.co.kr

Low Voltage 1.2V/1.8V CML 1:2 Fanout Buffer, 3.2Gbps, 3.2GHz

General Description

The SY54011R is a fully differential, low voltage 1.2V/1.8V CML 1:2 fanout buffer. It is optimized to provide two identical output copies with less than 15ps of skew and less than 10pspp total jitter. The SY54011R can process clock signals as fast as 3.2GHz or data patterns up to 3.2Gbps. The differential input includes Micrel’s unique, 3-pin input termination architecture that interfaces to LVPECL, LVDS or CML differential signals, (AC- or DC-coupled from a 2.5V driver) as small as 100m V (200m VPP) without any level-shifting or termination resistor networks in the signal path. For AC-coupled input interface applications, an integrated voltage reference (VREF-AC) is provided to bias the VT pin. The outputs are CML, with extremely fast rise/fall times guaranteed to be less than 95ps. The SY54011R operates from a 2.5V ±5% core supply and a 1.8V or 1.2V ±5% output supply and is guaranteed over the full industrial temperature range (- 40°C to +85°C). The SY54011R is part of Micrel’s ® high-speed, Precision Edge product line. Datasheets and support documentation can be found on Micrel’s web site at: .micrel..

Precision Edge

®

Features

∑ 1.2V/1.8V CML 1:2 fanout buffer ∑ Guaranteed AC performance over temperature and voltage:

- DC-to- > 3.2Gbps throughput

- <300ps propagation delay (IN-to-Q)

- <15ps within-device skew

- <95ps rise/fall times ∑ Ultra-low jitter design

- <1ps RMS cycle-to-cycle jitter

- <10ps PP total jitter

- <1ps RMS random jitter

- <10ps PP deterministic jitter ∑ High-speed CML outputs ∑ 2.5V ±5% , 1.8/1.2V ±5% power supply operation ∑ Industrial temperature range:

- 40°C to +85°C ® ∑ Available in 16-pin (3mm x 3mm) MLF package

Applications

∑ ∑ ∑ ∑ Data Distribution: OC-48, OC-48+FEC SONET clock and data distribution Fibre Channel clock and data distribution Gigabit Ethernet clock and data distribution

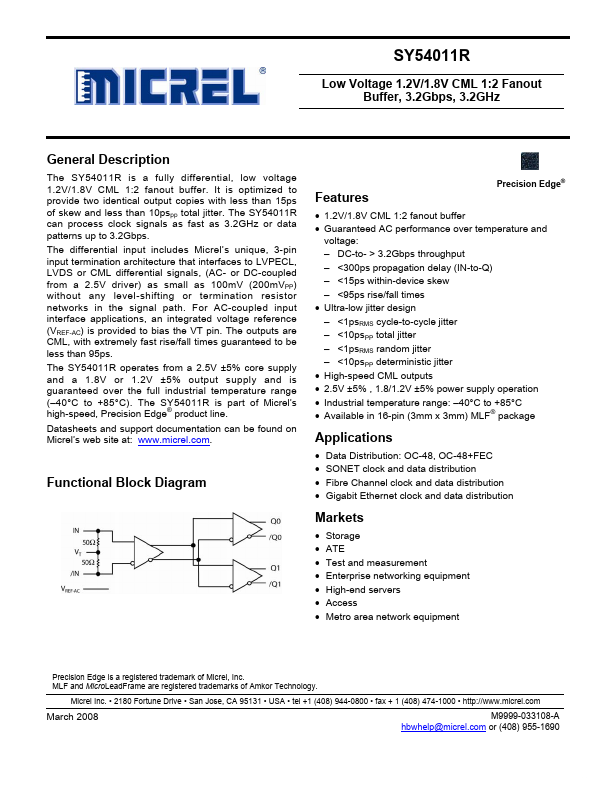

Functional Block Diagram

Markets

∑ ∑...